ເວເຟີ SiC 4H-N HPSI 6H-N 6H-P 3C-N SiC ເວເຟີ Epitaxial ສຳລັບ MOS ຫຼື SBD

ຊັ້ນໃຕ້ດິນ SiC SiC Epi-wafer ສະຫຼຸບ

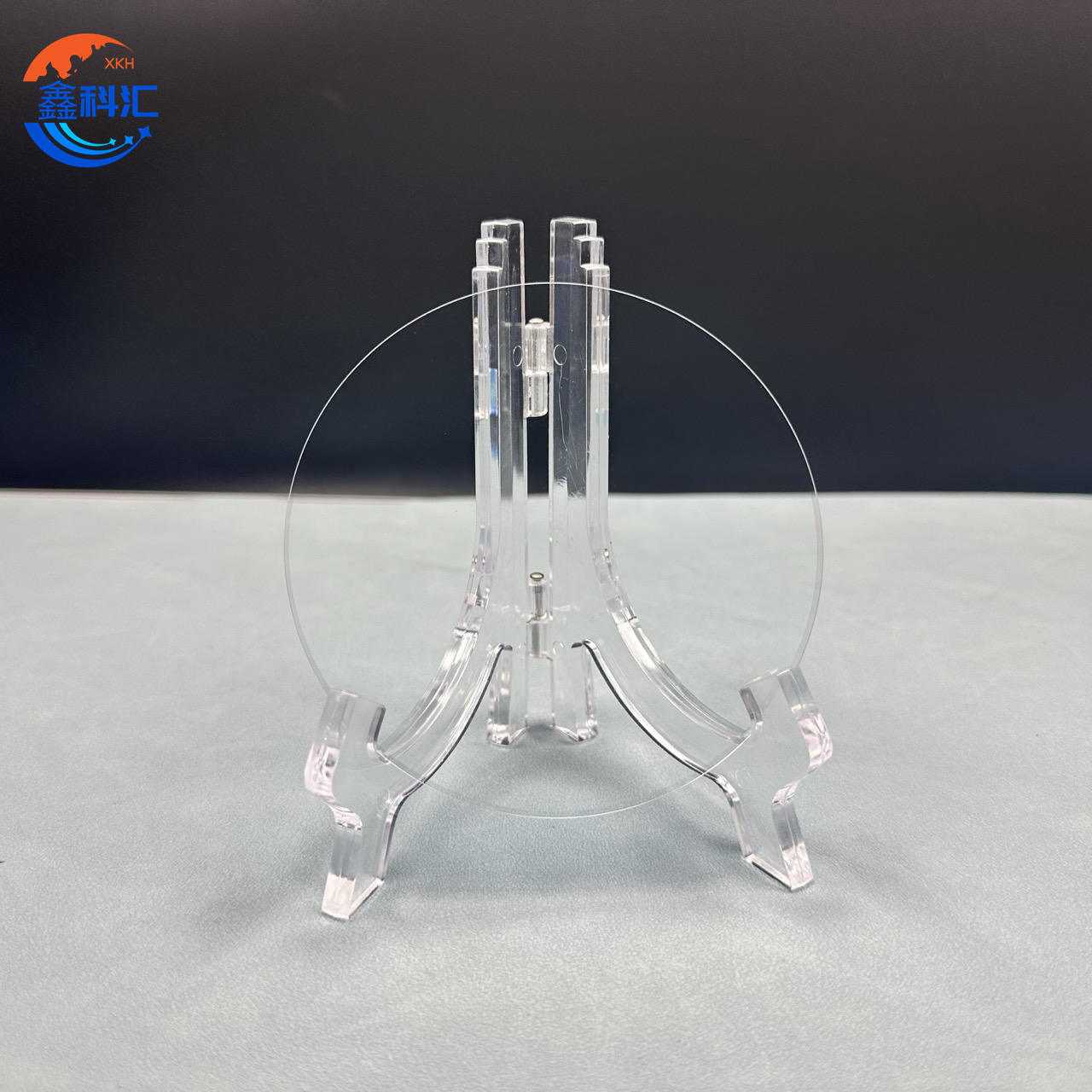

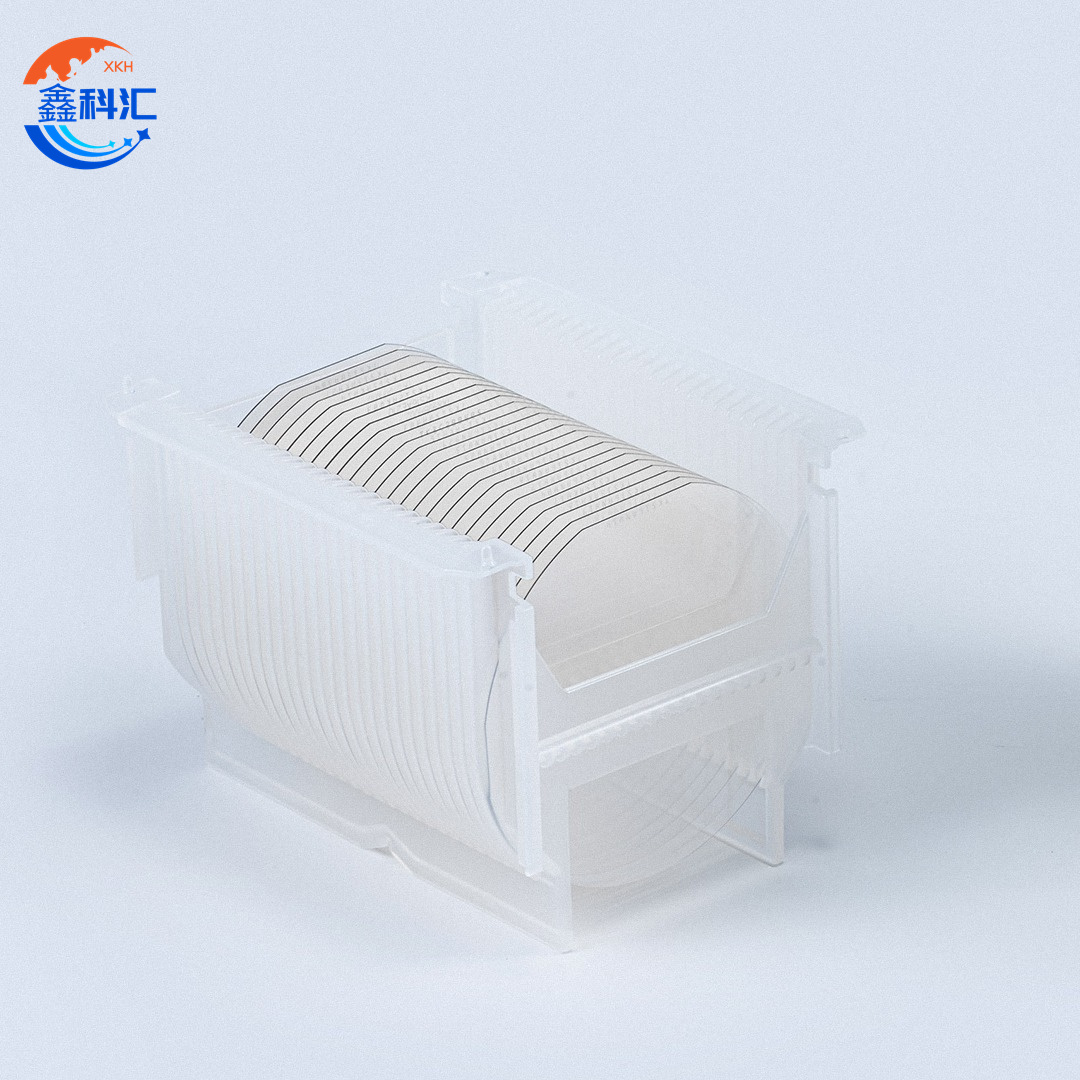

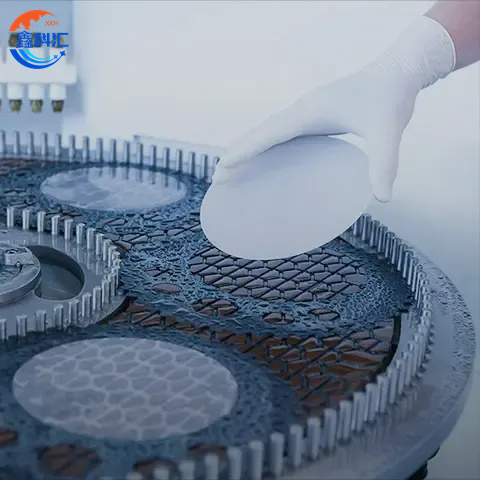

ພວກເຮົາສະເໜີຜະລິດຕະພັນທີ່ຄົບຊຸດຂອງວັດສະດຸ SiC ທີ່ມີຄຸນນະພາບສູງ ແລະ ເວເຟີ sic ໃນຫຼາຍຮູບແບບ ແລະ ໂປຣໄຟລ໌ການເສີມ — ລວມທັງ 4H-N (ວັດສະດຸນຳໄຟຟ້າປະເພດ n), 4H-P (ວັດສະດຸນຳໄຟຟ້າປະເພດ p), 4H-HPSI (ວັດສະດຸເຄິ່ງສນວນທີ່ມີຄວາມບໍລິສຸດສູງ), ແລະ 6H-P (ວັດສະດຸນຳໄຟຟ້າປະເພດ p) — ໃນເສັ້ນຜ່າສູນກາງຕັ້ງແຕ່ 4″, 6″, ແລະ 8″ ຈົນເຖິງ 12″. ນອກເໜືອໄປຈາກວັດສະດຸພື້ນຖານທີ່ເປົ່າ, ການບໍລິການເຕີບໂຕຂອງເວເຟີ epi ທີ່ມີມູນຄ່າເພີ່ມຂອງພວກເຮົາຍັງສະໜອງເວເຟີ epitaxial (epi) ທີ່ມີຄວາມໜາທີ່ຄວບຄຸມຢ່າງເຂັ້ມງວດ (1–20 µm), ຄວາມເຂັ້ມຂຸ້ນຂອງການເສີມ, ແລະ ຄວາມໜາແໜ້ນຂອງຂໍ້ບົກຜ່ອງ.

ແຜ່ນຊິບເວເຟີ ແລະ ແຜ່ນເອປິ ແຕ່ລະແຜ່ນໄດ້ຜ່ານການກວດກາໃນສາຍການຜະລິດຢ່າງເຂັ້ມງວດ (ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ <0.1 ຊມ⁻², ຄວາມຫຍາບຂອງພື້ນຜິວ Ra <0.2 nm) ແລະ ການວິເຄາະລັກສະນະທາງໄຟຟ້າຢ່າງຄົບຖ້ວນ (CV, ການສ້າງແຜນທີ່ຄວາມຕ້ານທານ) ເພື່ອຮັບປະກັນຄວາມສະໝໍ່າສະເໝີ ແລະ ປະສິດທິພາບຂອງຜລຶກທີ່ໂດດເດັ່ນ. ບໍ່ວ່າຈະໃຊ້ສຳລັບໂມດູນເອເລັກໂຕຣນິກພະລັງງານ, ເຄື່ອງຂະຫຍາຍສຽງ RF ຄວາມຖີ່ສູງ, ຫຼື ອຸປະກອນອອບໂຕເອເລັກໂຕຣນິກ (LEDs, ເຄື່ອງກວດຈັບແສງ), ສາຍຜະລິດຕະພັນຊັ້ນໃຕ້ດິນ SiC ແລະ ແຜ່ນເອປິ ຂອງພວກເຮົາໃຫ້ຄວາມໜ້າເຊື່ອຖື, ຄວາມໝັ້ນຄົງທາງຄວາມຮ້ອນ, ແລະ ຄວາມແຂງແຮງຂອງການແຕກຫັກທີ່ຕ້ອງການໂດຍການນຳໃຊ້ທີ່ຕ້ອງການຫຼາຍທີ່ສຸດໃນປະຈຸບັນ.

ຄຸນສົມບັດ ແລະ ການນຳໃຊ້ຂອງ SiC Substrate ປະເພດ 4H-N

-

ໂຄງສ້າງຊັ້ນຮອງ SiC 4H-N ແບບ Polytype (ຫົກຫລ່ຽມ)

ແບນວິດຊ່ອງກວ້າງຂອງ ~3.26 eV ຮັບປະກັນປະສິດທິພາບທາງໄຟຟ້າທີ່ໝັ້ນຄົງ ແລະ ຄວາມທົນທານທາງຄວາມຮ້ອນພາຍໃຕ້ເງື່ອນໄຂອຸນຫະພູມສູງ ແລະ ສະໜາມໄຟຟ້າສູງ.

-

ຊັ້ນຮອງພື້ນ SiCການໃຊ້ຢາຊູກຳລັງແບບ N

ການເສີມໄນໂຕຣເຈນທີ່ຄວບຄຸມໄດ້ຢ່າງແມ່ນຍຳເຮັດໃຫ້ມີຄວາມເຂັ້ມຂຸ້ນຂອງຕົວນຳຕັ້ງແຕ່ 1×10¹⁶ ຫາ 1×10¹⁹ cm⁻³ ແລະ ການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນໃນອຸນຫະພູມຫ້ອງສູງເຖິງ ~900 cm²/V·s, ເຊິ່ງຊ່ວຍຫຼຸດຜ່ອນການສູນເສຍການນຳໄຟຟ້າ.

-

ຊັ້ນຮອງພື້ນ SiCຄວາມຕ້ານທານກວ້າງ ແລະ ຄວາມເປັນເອກະພາບ

ຊ່ວງຄວາມຕ້ານທານທີ່ມີຢູ່ 0.01–10 Ω·cm ແລະ ຄວາມໜາຂອງແຜ່ນ wafer 350–650 µm ພ້ອມດ້ວຍຄວາມທົນທານ ±5% ທັງໃນດ້ານການເສີມ ແລະ ຄວາມໜາ—ເໝາະສຳລັບການຜະລິດອຸປະກອນພະລັງງານສູງ.

-

ຊັ້ນຮອງພື້ນ SiCຄວາມໜາແໜ້ນຂອງຂໍ້ບົກຜ່ອງຕໍ່າຫຼາຍ

ຄວາມໜາແໜ້ນຂອງທໍ່ຈຸນລະພາກ < 0.1 ຊມ⁻² ແລະ ຄວາມໜາແໜ້ນຂອງການເຄື່ອນທີ່ຂອງລະນາບພື້ນຖານ < 500 ຊມ⁻², ເຊິ່ງໃຫ້ຜົນຜະລິດອຸປະກອນ > 99% ແລະ ຄວາມສົມບູນຂອງຜລຶກທີ່ດີກວ່າ.

- ຊັ້ນຮອງພື້ນ SiCການນຳຄວາມຮ້ອນທີ່ໂດດເດັ່ນ

ຄວາມນຳຄວາມຮ້ອນສູງເຖິງ ~370 W/m·K ຊ່ວຍໃນການກຳຈັດຄວາມຮ້ອນຢ່າງມີປະສິດທິພາບ, ເພີ່ມຄວາມໜ້າເຊື່ອຖືຂອງອຸປະກອນ ແລະ ຄວາມໜາແໜ້ນຂອງພະລັງງານ.

-

ຊັ້ນຮອງພື້ນ SiCແອັບພລິເຄຊັນເປົ້າໝາຍ

MOSFETs SiC, ໄດໂອດ Schottky, ໂມດູນພະລັງງານ ແລະ ອຸປະກອນ RF ສຳລັບການຂັບເຄື່ອນຍານພາຫະນະໄຟຟ້າ, ອິນເວີເຕີແສງອາທິດ, ການຂັບເຄື່ອນອຸດສາຫະກຳ, ລະບົບດຶງ, ແລະ ຕະຫຼາດເອເລັກໂຕຣນິກພະລັງງານທີ່ຕ້ອງການຄວາມຕ້ອງການອື່ນໆ.

ລາຍລະອຽດຂອງແຜ່ນເວເຟີ SiC ປະເພດ 4H-N ຂະໜາດ 6 ນິ້ວ | ||

| ຊັບສິນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ຊັ້ນຮຽນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ | 149.5 ມມ - 150.0 ມມ | 149.5 ມມ - 150.0 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ | 350 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 350 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ນອກແກນ: 4.0° ໄປທາງ <1120> ± 0.5° | ນອກແກນ: 4.0° ໄປທາງ <1120> ± 0.5° |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | ≤ 0.2 ຊມ² | ≤ 15 ຊມ² |

| ຄວາມຕ້ານທານ | 0.015 - 0.024 Ω·ຊມ | 0.015 - 0.028 Ω·ຊມ |

| ທິດທາງຮາບພຽງຫຼັກ | [10-10] ± 50° | [10-10] ± 50° |

| ຄວາມຍາວຮາບພຽງຫຼັກ | 475 ມມ ± 2.0 ມມ | 475 ມມ ± 2.0 ມມ |

| ການຍົກເວັ້ນຂອບ | 3 ມມ | 3 ມມ |

| LTV/TIV / ໂບ / ວໍປ | ≤ 2.5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤ 1 nm | ໂປໂລຍ Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 ນາໂນແມັດ | ≤ 0.5 ນາໂນແມັດ |

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ |

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 0.1% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 3% |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 5% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວສະສົມ ≤ 1 ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥ 0.2 ມມ | ອະນຸຍາດໃຫ້ 7 ອັນ, ≤ 1 ມມ ແຕ່ລະອັນ |

| ການເຄື່ອນທີ່ຂອງສະກູທີ່ເຈາະເກຍ | < 500 ຊມ³ | < 500 ຊມ³ |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ||

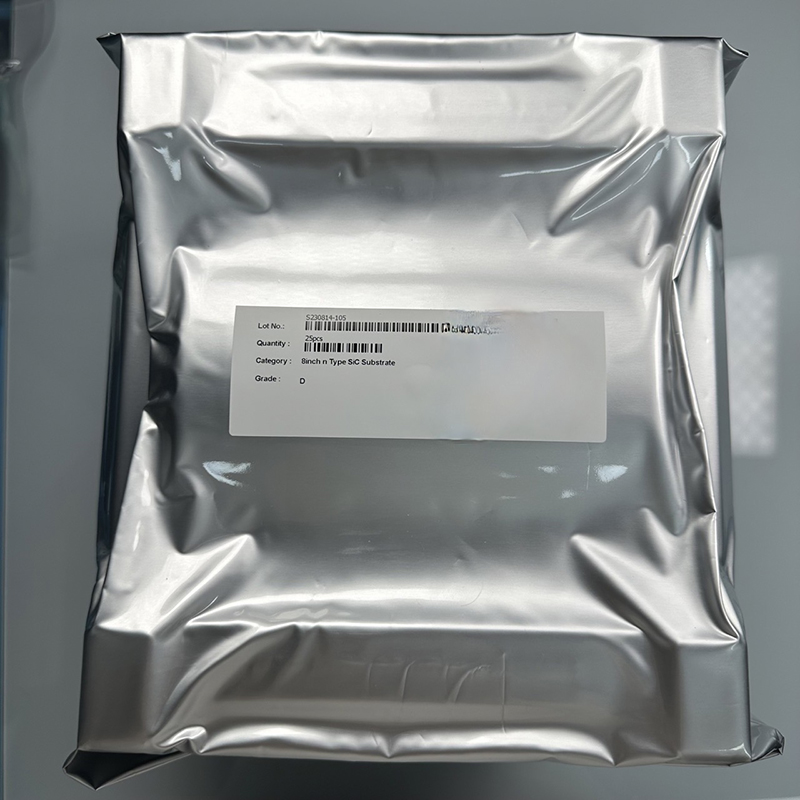

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ລາຍລະອຽດຂອງແຜ່ນເວເຟີ SiC ປະເພດ 4H-N ຂະໜາດ 8 ນິ້ວ | ||

| ຊັບສິນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ຊັ້ນຮຽນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ | 199.5 ມມ - 200.0 ມມ | 199.5 ມມ - 200.0 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | 4.0° ໄປຫາ <110> ± 0.5° | 4.0° ໄປຫາ <110> ± 0.5° |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | ≤ 0.2 ຊມ² | ≤ 5 ຊມ² |

| ຄວາມຕ້ານທານ | 0.015 - 0.025 Ω·ຊມ | 0.015 - 0.028 Ω·ຊມ |

| ທິດທາງອັນສູງສົ່ງ | ||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | 3 ມມ |

| LTV/TIV / ໂບ / ວໍປ | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤ 1 nm | ໂປໂລຍ Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 ນາໂນແມັດ | ≤ 0.5 ນາໂນແມັດ |

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ |

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 0.1% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 3% |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 5% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວສະສົມ ≤ 1 ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥ 0.2 ມມ | ອະນຸຍາດໃຫ້ 7 ອັນ, ≤ 1 ມມ ແຕ່ລະອັນ |

| ການເຄື່ອນທີ່ຂອງສະກູທີ່ເຈາະເກຍ | < 500 ຊມ³ | < 500 ຊມ³ |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ||

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

4H-SiC ເປັນວັດສະດຸປະສິດທິພາບສູງທີ່ໃຊ້ສຳລັບເອເລັກໂຕຣນິກພະລັງງານ, ອຸປະກອນ RF, ແລະ ການນຳໃຊ້ທີ່ມີອຸນຫະພູມສູງ. "4H" ໝາຍເຖິງໂຄງສ້າງຜລຶກ, ເຊິ່ງເປັນຮູບຫົກຫຼ່ຽມ, ແລະ "N" ໝາຍເຖິງປະເພດການເສີມທີ່ໃຊ້ເພື່ອເພີ່ມປະສິດທິພາບຂອງວັດສະດຸ.

ເທ4H-SiCປະເພດນີ້ມັກໃຊ້ສຳລັບ:

ເອເລັກໂຕຣນິກພະລັງງານ:ໃຊ້ໃນອຸປະກອນຕ່າງໆເຊັ່ນ: ໄດໂອດ, ມອສເຟດ, ແລະ IGBT ສຳລັບລະບົບສົ່ງກຳລັງລົດຍົນໄຟຟ້າ, ເຄື່ອງຈັກອຸດສາຫະກຳ ແລະ ລະບົບພະລັງງານທົດແທນ.

ເທັກໂນໂລຢີ 5G:ດ້ວຍຄວາມຕ້ອງການຂອງ 5G ສຳລັບອົງປະກອບຄວາມຖີ່ສູງ ແລະ ປະສິດທິພາບສູງ, ຄວາມສາມາດຂອງ SiC ໃນການຈັດການກັບແຮງດັນສູງ ແລະ ເຮັດວຽກຢູ່ໃນອຸນຫະພູມສູງເຮັດໃຫ້ມັນເໝາະສົມສຳລັບເຄື່ອງຂະຫຍາຍສັນຍານພະລັງງານສະຖານີຖານ ແລະ ອຸປະກອນ RF.

ລະບົບພະລັງງານແສງຕາເວັນ:ຄຸນສົມບັດການຈັດການພະລັງງານທີ່ດີເລີດຂອງ SiC ແມ່ນເໝາະສົມທີ່ສຸດສຳລັບຕົວປ່ຽນ ແລະ ຕົວແປງໄຟຟ້າທີ່ໃຊ້ພະລັງງານແສງຕາເວັນ.

ພາຫະນະໄຟຟ້າ (EVs):SiC ຖືກນຳໃຊ້ຢ່າງກວ້າງຂວາງໃນລະບົບສົ່ງກຳລັງລົດໄຟຟ້າ EV ສຳລັບການປ່ຽນພະລັງງານທີ່ມີປະສິດທິພາບຫຼາຍຂຶ້ນ, ການຜະລິດຄວາມຮ້ອນຕ່ຳລົງ, ແລະ ຄວາມໜາແໜ້ນຂອງພະລັງງານສູງຂຶ້ນ.

ຄຸນສົມບັດ ແລະ ການນຳໃຊ້ຂອງວັດສະດຸ SiC Substrate 4H ປະເພດເຄິ່ງສນວນ

ຄຸນສົມບັດ:

-

ເຕັກນິກການຄວບຄຸມຄວາມໜາແໜ້ນທີ່ບໍ່ມີທໍ່ນ້ອຍຮັບປະກັນການບໍ່ມີທໍ່ນ້ອຍໆ, ປັບປຸງຄຸນນະພາບຂອງຊັ້ນຮອງພື້ນ.

-

ເຕັກນິກການຄວບຄຸມແບບ monocrystallineຮັບປະກັນໂຄງສ້າງຜລຶກດຽວເພື່ອຄຸນສົມບັດຂອງວັດສະດຸທີ່ດີຂຶ້ນ.

-

ເຕັກນິກການຄວບຄຸມການລວມເຂົ້າກັນຫຼຸດຜ່ອນການມີສິ່ງເຈືອປົນ ຫຼື ສິ່ງປົນເປື້ອນ, ຮັບປະກັນໂຄງສ້າງທີ່ບໍລິສຸດ.

-

ເຕັກນິກການຄວບຄຸມຄວາມຕ້ານທານອະນຸຍາດໃຫ້ມີການຄວບຄຸມຄວາມຕ້ານທານທາງໄຟຟ້າໄດ້ຢ່າງຊັດເຈນ, ເຊິ່ງມີຄວາມສຳຄັນຫຼາຍຕໍ່ປະສິດທິພາບຂອງອຸປະກອນ.

-

ເຕັກນິກການຄວບຄຸມ ແລະ ຄວບຄຸມສິ່ງປົນເປື້ອນຄວບຄຸມ ແລະ ຈຳກັດການນຳເຂົ້າຂອງສິ່ງເຈືອປົນເພື່ອຮັກສາຄວາມສົມບູນຂອງຊັ້ນຮອງພື້ນ.

-

ເຕັກນິກການຄວບຄຸມຄວາມກວ້າງຂອງຂັ້ນຕອນຂອງພື້ນຜິວ: ໃຫ້ການຄວບຄຸມທີ່ຖືກຕ້ອງຕາມຄວາມກວ້າງຂອງຂັ້ນໄດ, ຮັບປະກັນຄວາມສອດຄ່ອງໃນທົ່ວຊັ້ນຮອງພື້ນ

ລາຍລະອຽດຂອງວັດສະດຸຮອງພື້ນ SiC 4H ຂະໜາດ 6 ນິ້ວ | ||

| ຊັບສິນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ (ມມ) | 145 ມມ - 150 ມມ | 145 ມມ - 150 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ (um) | 500 ± 15 | 500 ± 25 |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ເທິງແກນ: ±0.0001° | ເທິງແກນ: ±0.05° |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | ≤ 15 ຊມ-2 | ≤ 15 ຊມ-2 |

| ຄວາມຕ້ານທານ (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| ທິດທາງຮາບພຽງຫຼັກ | (0-10)° ± 5.0° | (10-10)° ± 5.0° |

| ຄວາມຍາວຮາບພຽງຫຼັກ | ຮອຍບາດ | ຮອຍບາດ |

| ການຍົກເວັ້ນຂອບ (ມມ) | ≤ 2.5 ໄມໂຄຣມ / ≤ 15 ໄມໂຄຣມ | ≤ 5.5 ໄມໂຄຣມ / ≤ 35 ໄມໂຄຣມ |

| LTV / ໂບວ / ວໍບ | ≤ 3 ໄມໂຄຣມ | ≤ 3 ໄມໂຄຣມ |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤ 1.5 µm | ໂປໂລຍ Ra ≤ 1.5 µm |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ≤ 20 ໄມໂຄຣມ | ≤ 60 ໄມໂຄຣມ |

| ແຜ່ນຄວາມຮ້ອນໂດຍແສງຄວາມເຂັ້ມສູງ | ສະສົມ ≤ 0.05% | ສະສົມ ≤ 3% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ ≤ 0.05% | ສະສົມ ≤ 3% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ≤ 0.05% | ສະສົມ ≤ 4% |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ (ຂະໜາດ) | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ > 02 ມມ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ > 02 ມມ |

| ການຂະຫຍາຍສະກູຊ່ວຍ | ≤ 500 ໄມໂຄຣມ | ≤ 500 ໄມໂຄຣມ |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ລາຍລະອຽດຂອງຊັ້ນໃຕ້ດິນ SiC 4H ຂະໜາດ 4 ນິ້ວ ແບບເຄິ່ງສນວນ

| ພາລາມິເຕີ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

|---|---|---|

| ຄຸນສົມບັດທາງກາຍະພາບ | ||

| ເສັ້ນຜ່າສູນກາງ | 99.5 ມມ – 100.0 ມມ | 99.5 ມມ – 100.0 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ | 500 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ເທິງແກນ: <600h > 0.5° | ເທິງແກນ: <000h > 0.5° |

| ຄຸນສົມບັດທາງໄຟຟ້າ | ||

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ (MPD) | ≤1 ຊມ⁻² | ≤15 ຊມ⁻² |

| ຄວາມຕ້ານທານ | ≥150 Ω·ຊມ | ≥1.5 Ω·ຊມ |

| ຄວາມທົນທານທາງເລຂາຄະນິດ | ||

| ທິດທາງຮາບພຽງຫຼັກ | (0x10) ± 5.0° | (0x10) ± 5.0° |

| ຄວາມຍາວຮາບພຽງຫຼັກ | 52.5 ມມ ± 2.0 ມມ | 52.5 ມມ ± 2.0 ມມ |

| ຄວາມຍາວຮາບພຽງຂັ້ນສອງ | 18.0 ມມ ± 2.0 ມມ | 18.0 ມມ ± 2.0 ມມ |

| ທິດທາງຮາບພຽງຂັ້ນສອງ | 90° CW ຈາກມຸມຮາບພຽງ ± 5.0° (Si ຫງາຍໜ້າຂຶ້ນ) | 90° CW ຈາກມຸມຮາບພຽງ ± 5.0° (Si ຫງາຍໜ້າຂຶ້ນ) |

| ການຍົກເວັ້ນຂອບ | 3 ມມ | 3 ມມ |

| LTV / TTV / Bow / Warp | ≤2.5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10 μm / ≤15 μm / ≤25 μm / ≤40 μm |

| ຄຸນນະພາບພື້ນຜິວ | ||

| ຄວາມຫຍາບຂອງພື້ນຜິວ (Polish Ra) | ≤1 ນາໂນແມັດ | ≤1 ນາໂນແມັດ |

| ຄວາມຫຍາບຂອງພື້ນຜິວ (CMP Ra) | ≤0.2 ນາໂນແມັດ | ≤0.2 ນາໂນແມັດ |

| ຮອຍແຕກຂອບ (ແສງຄວາມເຂັ້ມສູງ) | ບໍ່ໄດ້ຮັບອະນຸຍາດ | ຄວາມຍາວສະສົມ ≥10 ມມ, ຮອຍແຕກດຽວ ≤2 ມມ |

| ຂໍ້ບົກຜ່ອງຂອງແຜ່ນຫົກຫຼ່ຽມ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.1% |

| ພື້ນທີ່ລວມ Polytype | ບໍ່ໄດ້ຮັບອະນຸຍາດ | ພື້ນທີ່ສະສົມ ≤1% |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤1% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນ | ບໍ່ໄດ້ຮັບອະນຸຍາດ | ຄວາມຍາວສະສົມຂອງເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ ≤1 |

| ຊິບຂອບ | ບໍ່ອະນຸຍາດໃຫ້ໃຊ້ (ຄວາມກວ້າງ/ຄວາມເລິກ ≥0.2 ມມ) | ≤5 ຊິບ (ແຕ່ລະອັນ ≤1 ມມ) |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນ | ບໍ່ໄດ້ລະບຸ | ບໍ່ໄດ້ລະບຸ |

| ການຫຸ້ມຫໍ່ | ||

| ການຫຸ້ມຫໍ່ | ກ່ອງຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື |

ຄໍາຮ້ອງສະຫມັກ:

ເທຊັ້ນຮອງພື້ນ SiC 4H ເຄິ່ງສນວນສ່ວນໃຫຍ່ແມ່ນໃຊ້ໃນອຸປະກອນເອເລັກໂຕຣນິກພະລັງງານສູງ ແລະ ຄວາມຖີ່ສູງ, ໂດຍສະເພາະໃນພາກສະໜາມ RFວັດສະດຸເຫຼົ່ານີ້ແມ່ນມີຄວາມສໍາຄັນສໍາລັບການນໍາໃຊ້ຕ່າງໆລວມທັງລະບົບການສື່ສານໄມໂຄເວຟ, radar ອາເຣແບບ phased, ແລະເຄື່ອງກວດຈັບໄຟຟ້າໄຮ້ສາຍການນຳຄວາມຮ້ອນສູງ ແລະ ລັກສະນະທາງໄຟຟ້າທີ່ດີເລີດຂອງມັນເຮັດໃຫ້ພວກມັນເໝາະສົມສຳລັບການນຳໃຊ້ທີ່ຕ້ອງການຄວາມຕ້ອງການສູງໃນເອເລັກໂຕຣນິກພະລັງງານ ແລະ ລະບົບການສື່ສານ.

ຄຸນສົມບັດ ແລະ ການນຳໃຊ້ຂອງ SiC epi wafer 4H-N

ຄຸນສົມບັດ ແລະ ການນຳໃຊ້ຂອງ SiC 4H-N ປະເພດ Epi Wafer

ຄຸນສົມບັດຂອງ SiC 4H-N ປະເພດ Epi Wafer:

ສ່ວນປະກອບຂອງວັດສະດຸ:

SiC (ຊິລິຄອນຄາໄບດ໌)SiC ເປັນທີ່ຮູ້ຈັກກັນດີໃນດ້ານຄວາມແຂງທີ່ໂດດເດັ່ນ, ຄວາມນຳຄວາມຮ້ອນສູງ, ແລະ ຄຸນສົມບັດທາງໄຟຟ້າທີ່ດີເລີດ, ເໝາະສຳລັບອຸປະກອນເອເລັກໂຕຣນິກທີ່ມີປະສິດທິພາບສູງ.

ໂພລີໄທ 4H-SiCໂພລີໄທບ 4H-SiC ແມ່ນເປັນທີ່ຮູ້ຈັກກັນດີໃນດ້ານປະສິດທິພາບສູງ ແລະ ຄວາມໝັ້ນຄົງໃນການນຳໃຊ້ເອເລັກໂຕຣນິກ.

ການໂດບປະເພດ N: ການໂດບແບບ N (ໂດບດ້ວຍໄນໂຕຣເຈນ) ໃຫ້ການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນທີ່ດີເລີດ, ເຮັດໃຫ້ SiC ເໝາະສົມສຳລັບການນຳໃຊ້ຄວາມຖີ່ສູງ ແລະ ພະລັງງານສູງ.

ການນຳຄວາມຮ້ອນສູງ:

ແຜ່ນຊິລິໂຄນມີຄວາມນຳຄວາມຮ້ອນທີ່ດີກວ່າ, ໂດຍປົກກະຕິແມ່ນຕັ້ງແຕ່120–200 W/m·K, ເຊິ່ງຊ່ວຍໃຫ້ພວກເຂົາສາມາດຈັດການຄວາມຮ້ອນໃນອຸປະກອນພະລັງງານສູງເຊັ່ນ: ທຣານຊິດເຕີ ແລະ ໄດໂອດໄດ້ຢ່າງມີປະສິດທິພາບ.

ຊ່ອງຫວ່າງແບນວິດກວ້າງ:

ດ້ວຍຊ່ອງຫວ່າງແບນວິດຂອງ3.26 ອີວີ, 4H-SiC ສາມາດເຮັດວຽກໄດ້ໃນແຮງດັນ, ຄວາມຖີ່ ແລະ ອຸນຫະພູມທີ່ສູງກວ່າເມື່ອທຽບກັບອຸປະກອນທີ່ອີງໃສ່ຊິລິໂຄນແບບດັ້ງເດີມ, ເຮັດໃຫ້ມັນເໝາະສົມສຳລັບການນຳໃຊ້ທີ່ມີປະສິດທິພາບສູງ ແລະ ມີປະສິດຕິພາບສູງ.

ຄຸນສົມບັດທາງໄຟຟ້າ:

ການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນ ແລະ ຄວາມນຳໄຟຟ້າສູງຂອງ SiC ເຮັດໃຫ້ມັນເໝາະສົມສຳລັບເອເລັກໂຕຣນິກພະລັງງານ, ສະເໜີຄວາມໄວໃນການສະຫຼັບທີ່ໄວ ແລະ ຄວາມສາມາດໃນການຈັດການກະແສໄຟຟ້າ ແລະ ແຮງດັນສູງ, ເຊິ່ງເຮັດໃຫ້ລະບົບການຄຸ້ມຄອງພະລັງງານມີປະສິດທິພາບຫຼາຍຂຶ້ນ.

ຄວາມຕ້ານທານທາງກົນຈັກ ແລະ ສານເຄມີ:

SiC ເປັນໜຶ່ງໃນວັດສະດຸທີ່ແຂງທີ່ສຸດ, ເປັນອັນດັບສອງຮອງຈາກເພັດ, ແລະ ມີຄວາມທົນທານຕໍ່ການຜຸພັງ ແລະ ການກັດກ່ອນສູງ, ເຮັດໃຫ້ມັນທົນທານໃນສະພາບແວດລ້ອມທີ່ຮຸນແຮງ.

ການນຳໃຊ້ SiC 4H-N ປະເພດ Epi Wafer:

ເອເລັກໂຕຣນິກພະລັງງານ:

ເວເຟີປະເພດ SiC 4H-N ຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງໃນMOSFET ພະລັງງານ, IGBT, ແລະໄດໂອດສຳລັບການປ່ຽນພະລັງງານໃນລະບົບຕ່າງໆເຊັ່ນເຄື່ອງແປງພະລັງງານແສງອາທິດ, ພາຫະນະໄຟຟ້າ, ແລະລະບົບເກັບຮັກສາພະລັງງານ, ສະເໜີປະສິດທິພາບທີ່ດີຂຶ້ນ ແລະ ປະສິດທິພາບດ້ານພະລັງງານ.

ພາຫະນະໄຟຟ້າ (EVs):

In ລະບົບສົ່ງກຳລັງຂອງຍານພາຫະນະໄຟຟ້າ, ຕົວຄວບຄຸມມໍເຕີ, ແລະສະຖານີສາກໄຟ, ແຜ່ນຊິລິໂຄນຊ່ວຍໃຫ້ປະສິດທິພາບຂອງແບັດເຕີຣີດີຂຶ້ນ, ການສາກໄຟໄວຂຶ້ນ, ແລະ ປະສິດທິພາບພະລັງງານໂດຍລວມທີ່ດີຂຶ້ນ ເນື່ອງຈາກຄວາມສາມາດໃນການຮັບມືກັບພະລັງງານ ແລະ ອຸນຫະພູມສູງ.

ລະບົບພະລັງງານທົດແທນ:

ເຄື່ອງແປງໄຟຟ້າພະລັງງານແສງອາທິດ: ເວເຟີ SiC ຖືກນຳໃຊ້ໃນລະບົບພະລັງງານແສງຕາເວັນສຳລັບການປ່ຽນພະລັງງານ DC ຈາກແຜງໂຊລາເຊວໄປເປັນໄຟຟ້າ AC, ເຊິ່ງເພີ່ມປະສິດທິພາບ ແລະ ປະສິດທິພາບຂອງລະບົບໂດຍລວມ.

ກັງຫັນລົມເທັກໂນໂລຢີ SiC ຖືກນຳໃຊ້ໃນລະບົບຄວບຄຸມກັງຫັນລົມ, ການເພີ່ມປະສິດທິພາບການຜະລິດພະລັງງານ ແລະ ປະສິດທິພາບການປ່ຽນໄຟຟ້າ.

ອາວະກາດ ແລະ ປ້ອງກັນປະເທດ:

ແຜ່ນເວເຟີ SiC ແມ່ນເໝາະສົມທີ່ສຸດສຳລັບການນຳໃຊ້ໃນເອເລັກໂຕຣນິກການບິນອະວະກາດແລະການນຳໃຊ້ທາງທະຫານ, ລວມທັງລະບົບເຣດາແລະເອເລັກໂຕຣນິກດາວທຽມ, ບ່ອນທີ່ມີຄວາມຕ້ານທານລັງສີສູງ ແລະ ຄວາມໝັ້ນຄົງທາງຄວາມຮ້ອນແມ່ນມີຄວາມສຳຄັນຫຼາຍ.

ການນຳໃຊ້ທີ່ມີອຸນຫະພູມສູງ ແລະ ຄວາມຖີ່ສູງ:

ເວເຟີ SiC ເກັ່ງໃນເຄື່ອງໃຊ້ໄຟຟ້າທີ່ມີອຸນຫະພູມສູງ, ໃຊ້ໃນເຄື່ອງຈັກເຮືອບິນ, ຍານອະວະກາດ, ແລະລະບົບຄວາມຮ້ອນອຸດສາຫະກໍາ, ຍ້ອນວ່າພວກມັນຮັກສາປະສິດທິພາບໃນສະພາບຄວາມຮ້ອນທີ່ຮຸນແຮງ. ນອກຈາກນັ້ນ, bandgap ທີ່ກວ້າງຂວາງຂອງພວກມັນຍັງຊ່ວຍໃຫ້ສາມາດນໍາໃຊ້ໄດ້ໃນການນຳໃຊ້ຄວາມຖີ່ສູງຄືອຸປະກອນ RFແລະການສື່ສານດ້ວຍໄມໂຄເວຟ.

| ລາຍລະອຽດແກນ epit ປະເພດ N ຂະໜາດ 6 ນິ້ວ | |||

| ພາລາມິເຕີ | ໜ່ວຍ | Z-MOS | |

| ປະເພດ | ຄວາມເປັນມາ / ສານເຈືອປົນ | - | ປະເພດ N / ໄນໂຕຣເຈນ |

| ຊັ້ນບັບເຟີ | ຄວາມໜາຂອງຊັ້ນບັບເຟີ | um | 1 |

| ຄວາມທົນທານຂອງຄວາມໜາຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | ຊມ-3 | 1.00E+18 | |

| ຄວາມທົນທານຂອງຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຊັ້ນທີ 1 ຂອງ Epi | ຄວາມໜາຂອງຊັ້ນ Epi | um | 11.5 |

| ຄວາມໜາຂອງຊັ້ນ Epi ສະເໝີພາບ | % | ±4% | |

| ຄວາມທົນທານຂອງຊັ້ນ Epi ((Spec- ສູງສຸດ, ຕໍ່າສຸດ)/ສະເປັກ) | % | ±5% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi | ຊມ-3 | 1E 15~ 1E 18 | |

| ຄວາມທົນທານຕໍ່ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi | % | 6% | |

| ຄວາມສະໝໍ່າສະເໝີຂອງຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi (σ) / ສະເລ່ຍ) | % | ≤5% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi ທີ່ເປັນເອກະພາບ <(ສູງສຸດ-ຕໍ່າສຸດ)/(ສູງສຸດ+ຕໍ່າສຸດ> | % | ≤ 10% | |

| ຮູບຊົງເວເຟີ Epitaixal | ໂບ | um | ≤±20 |

| ວໍປ | um | ≤30 | |

| ໂທລະພາບທີວີ | um | ≤ 10 | |

| ອັດຕາດອກເບ້ຍຕໍ່າສຸດ (LTV) | um | ≤2 | |

| ລັກສະນະທົ່ວໄປ | ຄວາມຍາວຂອງຮອຍຂີດຂ່ວນ | mm | ≤30 ມມ |

| ຊິບຂອບ | - | ບໍ່ມີ | |

| ການກຳນົດຂໍ້ບົກຜ່ອງ | ≥97% (ວັດແທກດ້ວຍ 2*2, ຂໍ້ບົກຜ່ອງທີ່ຮ້າຍແຮງລວມມີ: ຂໍ້ບົກຜ່ອງປະກອບມີ ທໍ່ນ້ອຍ / ຂຸມໃຫຍ່, ແຄລອດ, ຮູບສາມຫຼ່ຽມ | ||

| ການປົນເປື້ອນຂອງໂລຫະ | ອະຕອມ/ຊມ² | ດຟຟລ ອິ ≤5E10 ອະຕອມ/ຊມ2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca ແລະ Mn) | |

| ແພັກເກດ | ລາຍລະອຽດການຫຸ້ມຫໍ່ | ຊິ້ນ/ກ່ອງ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

| ລາຍລະອຽດສະເພາະ epitaxial ປະເພດ N ຂະໜາດ 8 ນິ້ວ | |||

| ພາລາມິເຕີ | ໜ່ວຍ | Z-MOS | |

| ປະເພດ | ຄວາມເປັນມາ / ສານເຈືອປົນ | - | ປະເພດ N / ໄນໂຕຣເຈນ |

| ຊັ້ນບັບເຟີ | ຄວາມໜາຂອງຊັ້ນບັບເຟີ | um | 1 |

| ຄວາມທົນທານຂອງຄວາມໜາຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | ຊມ-3 | 1.00E+18 | |

| ຄວາມທົນທານຂອງຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຊັ້ນທີ 1 ຂອງ Epi | ຄວາມໜາຂອງຊັ້ນ Epi ໂດຍສະເລ່ຍ | um | 8~ 12 |

| ຄວາມໜາຂອງຊັ້ນ Epi ທີ່ເປັນເອກະພາບ (σ/ສະເລ່ຍ) | % | ≤2.0 | |

| ຄວາມທົນທານຂອງຊັ້ນ Epi ((Spec -Max,Min)/Spec) | % | ±6 | |

| ການໃຊ້ສານກະຕຸ້ນໂດຍສະເລ່ຍສຸດທິຂອງຊັ້ນ Epi | ຊມ-3 | 8E+15 ~2E+16 | |

| ຄວາມສະໝໍ່າສະເໝີຂອງສານເສີມສຸດທິຂອງຊັ້ນ Epi (σ/ສະເລ່ຍ) | % | ≤5 | |

| ຊັ້ນ Epi ຄວາມທົນທານຕໍ່ການໃຊ້ຢາເສີມສຸດທິ ((Spec -Max, | % | ± 10.0 | |

| ຮູບຊົງເວເຟີ Epitaixal | ໄມລ໌)/ຊ) ບິດງໍ | um | ≤50.0 |

| ໂບ | um | ± 30.0 | |

| ໂທລະພາບທີວີ | um | ≤ 10.0 | |

| ອັດຕາດອກເບ້ຍຕໍ່າສຸດ (LTV) | um | ≤4.0 (10 ມມ × 10 ມມ) | |

| ທົ່ວໄປ ລັກສະນະ | ຮອຍຂີດຂ່ວນ | - | ຄວາມຍາວສະສົມ≤ 1/2 ເສັ້ນຜ່າສູນກາງແຜ່ນ |

| ຊິບຂອບ | - | ≤2 ຊິບ, ແຕ່ລະລັດສະໝີ ≤1.5 ມມ | |

| ການປົນເປື້ອນໂລຫະພື້ນຜິວ | ອະຕອມ/ຊມ2 | ≤5E10 ອະຕອມ/ຊມ2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca ແລະ Mn) | |

| ການກວດກາຂໍ້ບົກພ່ອງ | % | ≥ 96.0 (ຂໍ້ບົກຜ່ອງ 2X2 ປະກອບມີທໍ່ນ້ອຍ / ຂຸມໃຫຍ່, ແຄລອດ, ຂໍ້ບົກຜ່ອງສາມຫຼ່ຽມ, ການຕົກລົງ, ເສັ້ນຊື່/IGSF-s, BPD) | |

| ການປົນເປື້ອນໂລຫະພື້ນຜິວ | ອະຕອມ/ຊມ2 | ≤5E10 ອະຕອມ/ຊມ2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca ແລະ Mn) | |

| ແພັກເກດ | ລາຍລະອຽດການຫຸ້ມຫໍ່ | - | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ຄຳຖາມ ແລະ ຄຳຕອບກ່ຽວກັບແຜ່ນຊີຊີ

ຄຳຖາມທີ 1: ຂໍ້ໄດ້ປຽບຫຼັກຂອງການໃຊ້ແຜ່ນ SiC ທຽບກັບແຜ່ນຊິລິໂຄນແບບດັ້ງເດີມໃນເຄື່ອງໃຊ້ໄຟຟ້າແມ່ນຫຍັງ?

ກ1:

ເວເຟີ SiC ມີຂໍ້ໄດ້ປຽບທີ່ສຳຄັນຫຼາຍຢ່າງທຽບກັບເວເຟີຊິລິໂຄນ (Si) ແບບດັ້ງເດີມໃນເອເລັກໂຕຣນິກພະລັງງານ, ລວມທັງ:

ປະສິດທິພາບສູງຂຶ້ນ: SiC ມີແຖບຄວາມຖີ່ກວ້າງກວ່າ (3.26 eV) ເມື່ອທຽບກັບຊິລິກອນ (1.1 eV), ເຊິ່ງຊ່ວຍໃຫ້ອຸປະກອນຕ່າງໆສາມາດເຮັດວຽກໄດ້ໃນແຮງດັນ, ຄວາມຖີ່ ແລະ ອຸນຫະພູມທີ່ສູງຂຶ້ນ. ສິ່ງນີ້ເຮັດໃຫ້ການສູນເສຍພະລັງງານຕ່ຳລົງ ແລະ ປະສິດທິພາບສູງຂຶ້ນໃນລະບົບການປ່ຽນແປງພະລັງງານ.

ການນຳຄວາມຮ້ອນສູງຄວາມນຳຄວາມຮ້ອນຂອງ SiC ສູງກວ່າຊິລິໂຄນຫຼາຍ, ເຊິ່ງເຮັດໃຫ້ການລະບາຍຄວາມຮ້ອນດີຂຶ້ນໃນການນຳໃຊ້ພະລັງງານສູງ, ເຊິ່ງຊ່ວຍປັບປຸງຄວາມໜ້າເຊື່ອຖື ແລະ ອາຍຸການໃຊ້ງານຂອງອຸປະກອນໄຟຟ້າ.

ແຮງດັນໄຟຟ້າ ແລະ ການຈັດການກະແສໄຟຟ້າທີ່ສູງຂຶ້ນອຸປະກອນ SiC ສາມາດຮັບມືກັບລະດັບແຮງດັນ ແລະ ກະແສໄຟຟ້າທີ່ສູງຂຶ້ນ, ເຮັດໃຫ້ພວກມັນເໝາະສົມກັບການນຳໃຊ້ພະລັງງານສູງ ເຊັ່ນ: ພາຫະນະໄຟຟ້າ, ລະບົບພະລັງງານທົດແທນ, ແລະ ລະບົບຂັບເຄື່ອນມໍເຕີອຸດສາຫະກຳ.

ຄວາມໄວໃນການສະຫຼັບທີ່ໄວຂຶ້ນອຸປະກອນ SiC ມີຄວາມສາມາດສະຫຼັບໄດ້ໄວຂຶ້ນ, ເຊິ່ງປະກອບສ່ວນເຂົ້າໃນການຫຼຸດຜ່ອນການສູນເສຍພະລັງງານ ແລະ ຂະໜາດຂອງລະບົບ, ເຮັດໃຫ້ພວກມັນເໝາະສົມສຳລັບການນຳໃຊ້ຄວາມຖີ່ສູງ.

ຄຳຖາມທີ 2: ການນຳໃຊ້ແຜ່ນ SiC ຫຼັກໆໃນອຸດສາຫະກຳລົດຍົນແມ່ນຫຍັງ?

A2:

ໃນອຸດສາຫະກໍາລົດຍົນ, ແຜ່ນຊິລິໂຄນ SiC ຖືກນໍາໃຊ້ຕົ້ນຕໍໃນ:

ລະບົບສົ່ງກຳລັງລົດໄຟຟ້າ (EV)ສ່ວນປະກອບທີ່ອີງໃສ່ SiC ເຊັ່ນອິນເວີເຕີແລະMOSFET ພະລັງງານປັບປຸງປະສິດທິພາບ ແລະ ປະສິດທິພາບຂອງລະບົບສົ່ງກຳລັງຂອງຍານພາຫະນະໄຟຟ້າໂດຍການເຮັດໃຫ້ຄວາມໄວໃນການສະຫຼັບໄວຂຶ້ນ ແລະ ຄວາມໜາແໜ້ນຂອງພະລັງງານສູງຂຶ້ນ. ສິ່ງນີ້ນຳໄປສູ່ອາຍຸການໃຊ້ງານຂອງແບັດເຕີຣີທີ່ຍາວນານຂຶ້ນ ແລະ ປະສິດທິພາບໂດຍລວມຂອງຍານພາຫະນະທີ່ດີຂຶ້ນ.

ເຄື່ອງສາກໄຟໃນຕົວອຸປະກອນ SiC ຊ່ວຍປັບປຸງປະສິດທິພາບຂອງລະບົບສາກໄຟໃນຕົວລົດໂດຍການເຮັດໃຫ້ເວລາສາກໄຟໄວຂຶ້ນ ແລະ ການຈັດການຄວາມຮ້ອນທີ່ດີຂຶ້ນ, ເຊິ່ງເປັນສິ່ງສຳຄັນສຳລັບລົດໄຟຟ້າເພື່ອຮອງຮັບສະຖານີສາກໄຟພະລັງງານສູງ.

ລະບົບການຈັດການແບັດເຕີຣີ (BMS)ເທັກໂນໂລຢີ SiC ຊ່ວຍປັບປຸງປະສິດທິພາບຂອງລະບົບການຈັດການແບັດເຕີຣີ, ເຊິ່ງຊ່ວຍໃຫ້ການຄວບຄຸມແຮງດັນໄຟຟ້າດີຂຶ້ນ, ການຈັດການພະລັງງານທີ່ສູງຂຶ້ນ, ແລະ ອາຍຸການໃຊ້ງານຂອງແບັດເຕີຣີທີ່ຍາວນານຂຶ້ນ.

ຕົວແປງ DC-DC: ເວເຟີ SiC ຖືກນຳໃຊ້ໃນຕົວແປງ DC-DCເພື່ອປ່ຽນພະລັງງານ DC ແຮງດັນສູງໄປເປັນພະລັງງານ DC ແຮງດັນຕ່ຳໃຫ້ມີປະສິດທິພາບຫຼາຍຂຶ້ນ, ເຊິ່ງເປັນສິ່ງສຳຄັນໃນລົດຍົນໄຟຟ້າເພື່ອຈັດການພະລັງງານຈາກແບັດເຕີຣີໄປຫາອົງປະກອບຕ່າງໆໃນລົດ.

ປະສິດທິພາບທີ່ດີເລີດຂອງ SiC ໃນການນຳໃຊ້ແຮງດັນສູງ, ອຸນຫະພູມສູງ ແລະ ປະສິດທິພາບສູງເຮັດໃຫ້ມັນມີຄວາມຈຳເປັນສຳລັບການຫັນປ່ຽນຂອງອຸດສາຫະກຳລົດຍົນໄປສູ່ການເຄື່ອນທີ່ດ້ວຍໄຟຟ້າ.

ລາຍລະອຽດຂອງແຜ່ນເວເຟີ SiC ປະເພດ 4H-N ຂະໜາດ 6 ນິ້ວ | ||

| ຊັບສິນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ຊັ້ນຮຽນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ | 149.5 ມມ – 150.0 ມມ | 149.5 ມມ – 150.0 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ | 350 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 350 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ນອກແກນ: 4.0° ໄປທາງ <1120> ± 0.5° | ນອກແກນ: 4.0° ໄປທາງ <1120> ± 0.5° |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | ≤ 0.2 ຊມ² | ≤ 15 ຊມ² |

| ຄວາມຕ້ານທານ | 0.015 – 0.024 Ω·ຊມ | 0.015 – 0.028 Ω·ຊມ |

| ທິດທາງຮາບພຽງຫຼັກ | [10-10] ± 50° | [10-10] ± 50° |

| ຄວາມຍາວຮາບພຽງຫຼັກ | 475 ມມ ± 2.0 ມມ | 475 ມມ ± 2.0 ມມ |

| ການຍົກເວັ້ນຂອບ | 3 ມມ | 3 ມມ |

| LTV/TIV / ໂບ / ວໍປ | ≤ 2.5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤ 1 nm | ໂປໂລຍ Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 ນາໂນແມັດ | ≤ 0.5 ນາໂນແມັດ |

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ |

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 0.1% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 3% |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 5% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວສະສົມ ≤ 1 ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥ 0.2 ມມ | ອະນຸຍາດໃຫ້ 7 ອັນ, ≤ 1 ມມ ແຕ່ລະອັນ |

| ການເຄື່ອນທີ່ຂອງສະກູທີ່ເຈາະເກຍ | < 500 ຊມ³ | < 500 ຊມ³ |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ||

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ລາຍລະອຽດຂອງແຜ່ນເວເຟີ SiC ປະເພດ 4H-N ຂະໜາດ 8 ນິ້ວ | ||

| ຊັບສິນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ຊັ້ນຮຽນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ | 199.5 ມມ – 200.0 ມມ | 199.5 ມມ – 200.0 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | 4.0° ໄປຫາ <110> ± 0.5° | 4.0° ໄປຫາ <110> ± 0.5° |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | ≤ 0.2 ຊມ² | ≤ 5 ຊມ² |

| ຄວາມຕ້ານທານ | 0.015 – 0.025 Ω·ຊມ | 0.015 – 0.028 Ω·ຊມ |

| ທິດທາງອັນສູງສົ່ງ | ||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | 3 ມມ |

| LTV/TIV / ໂບ / ວໍປ | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤ 1 nm | ໂປໂລຍ Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 ນາໂນແມັດ | ≤ 0.5 ນາໂນແມັດ |

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ | ຄວາມຍາວລວມ ≤ 20 ມມ ຄວາມຍາວດ່ຽວ ≤ 2 ມມ |

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 0.1% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 3% |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 5% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ຄວາມຍາວສະສົມ ≤ 1 ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥ 0.2 ມມ | ອະນຸຍາດໃຫ້ 7 ອັນ, ≤ 1 ມມ ແຕ່ລະອັນ |

| ການເຄື່ອນທີ່ຂອງສະກູທີ່ເຈາະເກຍ | < 500 ຊມ³ | < 500 ຊມ³ |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ||

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ລາຍລະອຽດຂອງວັດສະດຸຮອງພື້ນ SiC 4H ຂະໜາດ 6 ນິ້ວ | ||

| ຊັບສິນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ (ມມ) | 145 ມມ – 150 ມມ | 145 ມມ – 150 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ (um) | 500 ± 15 | 500 ± 25 |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ເທິງແກນ: ±0.0001° | ເທິງແກນ: ±0.05° |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | ≤ 15 ຊມ-2 | ≤ 15 ຊມ-2 |

| ຄວາມຕ້ານທານ (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| ທິດທາງຮາບພຽງຫຼັກ | (0-10)° ± 5.0° | (10-10)° ± 5.0° |

| ຄວາມຍາວຮາບພຽງຫຼັກ | ຮອຍບາດ | ຮອຍບາດ |

| ການຍົກເວັ້ນຂອບ (ມມ) | ≤ 2.5 ໄມໂຄຣມ / ≤ 15 ໄມໂຄຣມ | ≤ 5.5 ໄມໂຄຣມ / ≤ 35 ໄມໂຄຣມ |

| LTV / ໂບວ / ວໍບ | ≤ 3 ໄມໂຄຣມ | ≤ 3 ໄມໂຄຣມ |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤ 1.5 µm | ໂປໂລຍ Ra ≤ 1.5 µm |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ≤ 20 ໄມໂຄຣມ | ≤ 60 ໄມໂຄຣມ |

| ແຜ່ນຄວາມຮ້ອນໂດຍແສງຄວາມເຂັ້ມສູງ | ສະສົມ ≤ 0.05% | ສະສົມ ≤ 3% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ ≤ 0.05% | ສະສົມ ≤ 3% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ≤ 0.05% | ສະສົມ ≤ 4% |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ (ຂະໜາດ) | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ > 02 ມມ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ > 02 ມມ |

| ການຂະຫຍາຍສະກູຊ່ວຍ | ≤ 500 ໄມໂຄຣມ | ≤ 500 ໄມໂຄຣມ |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ລາຍລະອຽດຂອງຊັ້ນໃຕ້ດິນ SiC 4H ຂະໜາດ 4 ນິ້ວ ແບບເຄິ່ງສນວນ

| ພາລາມິເຕີ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນ D (ຊັ້ນ D) |

|---|---|---|

| ຄຸນສົມບັດທາງກາຍະພາບ | ||

| ເສັ້ນຜ່າສູນກາງ | 99.5 ມມ – 100.0 ມມ | 99.5 ມມ – 100.0 ມມ |

| ແບບຫຼາຍຊັ້ນ | 4H | 4H |

| ຄວາມໜາ | 500 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ເທິງແກນ: <600h > 0.5° | ເທິງແກນ: <000h > 0.5° |

| ຄຸນສົມບັດທາງໄຟຟ້າ | ||

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ (MPD) | ≤1 ຊມ⁻² | ≤15 ຊມ⁻² |

| ຄວາມຕ້ານທານ | ≥150 Ω·ຊມ | ≥1.5 Ω·ຊມ |

| ຄວາມທົນທານທາງເລຂາຄະນິດ | ||

| ທິດທາງຮາບພຽງຫຼັກ | (0 × 10) ± 5.0° | (0 × 10) ± 5.0° |

| ຄວາມຍາວຮາບພຽງຫຼັກ | 52.5 ມມ ± 2.0 ມມ | 52.5 ມມ ± 2.0 ມມ |

| ຄວາມຍາວຮາບພຽງຂັ້ນສອງ | 18.0 ມມ ± 2.0 ມມ | 18.0 ມມ ± 2.0 ມມ |

| ທິດທາງຮາບພຽງຂັ້ນສອງ | 90° CW ຈາກມຸມຮາບພຽງ ± 5.0° (Si ຫງາຍໜ້າຂຶ້ນ) | 90° CW ຈາກມຸມຮາບພຽງ ± 5.0° (Si ຫງາຍໜ້າຂຶ້ນ) |

| ການຍົກເວັ້ນຂອບ | 3 ມມ | 3 ມມ |

| LTV / TTV / Bow / Warp | ≤2.5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10 μm / ≤15 μm / ≤25 μm / ≤40 μm |

| ຄຸນນະພາບພື້ນຜິວ | ||

| ຄວາມຫຍາບຂອງພື້ນຜິວ (Polish Ra) | ≤1 ນາໂນແມັດ | ≤1 ນາໂນແມັດ |

| ຄວາມຫຍາບຂອງພື້ນຜິວ (CMP Ra) | ≤0.2 ນາໂນແມັດ | ≤0.2 ນາໂນແມັດ |

| ຮອຍແຕກຂອບ (ແສງຄວາມເຂັ້ມສູງ) | ບໍ່ໄດ້ຮັບອະນຸຍາດ | ຄວາມຍາວສະສົມ ≥10 ມມ, ຮອຍແຕກດຽວ ≤2 ມມ |

| ຂໍ້ບົກຜ່ອງຂອງແຜ່ນຫົກຫຼ່ຽມ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.1% |

| ພື້ນທີ່ລວມ Polytype | ບໍ່ໄດ້ຮັບອະນຸຍາດ | ພື້ນທີ່ສະສົມ ≤1% |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤1% |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນ | ບໍ່ໄດ້ຮັບອະນຸຍາດ | ຄວາມຍາວສະສົມຂອງເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ ≤1 |

| ຊິບຂອບ | ບໍ່ອະນຸຍາດໃຫ້ໃຊ້ (ຄວາມກວ້າງ/ຄວາມເລິກ ≥0.2 ມມ) | ≤5 ຊິບ (ແຕ່ລະອັນ ≤1 ມມ) |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນ | ບໍ່ໄດ້ລະບຸ | ບໍ່ໄດ້ລະບຸ |

| ການຫຸ້ມຫໍ່ | ||

| ການຫຸ້ມຫໍ່ | ກ່ອງຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື |

| ລາຍລະອຽດແກນ epit ປະເພດ N ຂະໜາດ 6 ນິ້ວ | |||

| ພາລາມິເຕີ | ໜ່ວຍ | Z-MOS | |

| ປະເພດ | ຄວາມເປັນມາ / ສານເຈືອປົນ | - | ປະເພດ N / ໄນໂຕຣເຈນ |

| ຊັ້ນບັບເຟີ | ຄວາມໜາຂອງຊັ້ນບັບເຟີ | um | 1 |

| ຄວາມທົນທານຂອງຄວາມໜາຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | ຊມ-3 | 1.00E+18 | |

| ຄວາມທົນທານຂອງຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຊັ້ນທີ 1 ຂອງ Epi | ຄວາມໜາຂອງຊັ້ນ Epi | um | 11.5 |

| ຄວາມໜາຂອງຊັ້ນ Epi ສະເໝີພາບ | % | ±4% | |

| ຄວາມທົນທານຂອງຊັ້ນ Epi ((Spec- ສູງສຸດ, ຕໍ່າສຸດ)/ສະເປັກ) | % | ±5% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi | ຊມ-3 | 1E 15~ 1E 18 | |

| ຄວາມທົນທານຕໍ່ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi | % | 6% | |

| ຄວາມສະໝໍ່າສະເໝີຂອງຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi (σ) / ສະເລ່ຍ) | % | ≤5% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນ Epi ທີ່ເປັນເອກະພາບ <(ສູງສຸດ-ຕໍ່າສຸດ)/(ສູງສຸດ+ຕໍ່າສຸດ> | % | ≤ 10% | |

| ຮູບຊົງເວເຟີ Epitaixal | ໂບ | um | ≤±20 |

| ວໍປ | um | ≤30 | |

| ໂທລະພາບທີວີ | um | ≤ 10 | |

| ອັດຕາດອກເບ້ຍຕໍ່າສຸດ (LTV) | um | ≤2 | |

| ລັກສະນະທົ່ວໄປ | ຄວາມຍາວຂອງຮອຍຂີດຂ່ວນ | mm | ≤30 ມມ |

| ຊິບຂອບ | - | ບໍ່ມີ | |

| ການກຳນົດຂໍ້ບົກຜ່ອງ | ≥97% (ວັດແທກດ້ວຍ 2*2, ຂໍ້ບົກຜ່ອງທີ່ຮ້າຍແຮງລວມມີ: ຂໍ້ບົກຜ່ອງປະກອບມີ ທໍ່ນ້ອຍ / ຂຸມໃຫຍ່, ແຄລອດ, ຮູບສາມຫຼ່ຽມ | ||

| ການປົນເປື້ອນຂອງໂລຫະ | ອະຕອມ/ຊມ² | ດຟຟລ ອິ ≤5E10 ອະຕອມ/ຊມ2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca ແລະ Mn) | |

| ແພັກເກດ | ລາຍລະອຽດການຫຸ້ມຫໍ່ | ຊິ້ນ/ກ່ອງ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

| ລາຍລະອຽດສະເພາະ epitaxial ປະເພດ N ຂະໜາດ 8 ນິ້ວ | |||

| ພາລາມິເຕີ | ໜ່ວຍ | Z-MOS | |

| ປະເພດ | ຄວາມເປັນມາ / ສານເຈືອປົນ | - | ປະເພດ N / ໄນໂຕຣເຈນ |

| ຊັ້ນບັບເຟີ | ຄວາມໜາຂອງຊັ້ນບັບເຟີ | um | 1 |

| ຄວາມທົນທານຂອງຄວາມໜາຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | ຊມ-3 | 1.00E+18 | |

| ຄວາມທົນທານຂອງຄວາມເຂັ້ມຂຸ້ນຂອງຊັ້ນບັຟເຟີ | % | ±20% | |

| ຊັ້ນທີ 1 ຂອງ Epi | ຄວາມໜາຂອງຊັ້ນ Epi ໂດຍສະເລ່ຍ | um | 8~ 12 |

| ຄວາມໜາຂອງຊັ້ນ Epi ທີ່ເປັນເອກະພາບ (σ/ສະເລ່ຍ) | % | ≤2.0 | |

| ຄວາມທົນທານຂອງຊັ້ນ Epi ((Spec -Max,Min)/Spec) | % | ±6 | |

| ການໃຊ້ສານກະຕຸ້ນໂດຍສະເລ່ຍສຸດທິຂອງຊັ້ນ Epi | ຊມ-3 | 8E+15 ~2E+16 | |

| ຄວາມສະໝໍ່າສະເໝີຂອງສານເສີມສຸດທິຂອງຊັ້ນ Epi (σ/ສະເລ່ຍ) | % | ≤5 | |

| ຊັ້ນ Epi ຄວາມທົນທານຕໍ່ການໃຊ້ຢາເສີມສຸດທິ ((Spec -Max, | % | ± 10.0 | |

| ຮູບຊົງເວເຟີ Epitaixal | ໄມລ໌)/ຊ) ບິດງໍ | um | ≤50.0 |

| ໂບ | um | ± 30.0 | |

| ໂທລະພາບທີວີ | um | ≤ 10.0 | |

| ອັດຕາດອກເບ້ຍຕໍ່າສຸດ (LTV) | um | ≤4.0 (10 ມມ × 10 ມມ) | |

| ທົ່ວໄປ ລັກສະນະ | ຮອຍຂີດຂ່ວນ | - | ຄວາມຍາວສະສົມ≤ 1/2 ເສັ້ນຜ່າສູນກາງແຜ່ນ |

| ຊິບຂອບ | - | ≤2 ຊິບ, ແຕ່ລະລັດສະໝີ ≤1.5 ມມ | |

| ການປົນເປື້ອນໂລຫະພື້ນຜິວ | ອະຕອມ/ຊມ2 | ≤5E10 ອະຕອມ/ຊມ2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca ແລະ Mn) | |

| ການກວດກາຂໍ້ບົກພ່ອງ | % | ≥ 96.0 (ຂໍ້ບົກຜ່ອງ 2X2 ປະກອບມີທໍ່ນ້ອຍ / ຂຸມໃຫຍ່, ແຄລອດ, ຂໍ້ບົກຜ່ອງສາມຫຼ່ຽມ, ການຕົກລົງ, ເສັ້ນຊື່/IGSF-s, BPD) | |

| ການປົນເປື້ອນໂລຫະພື້ນຜິວ | ອະຕອມ/ຊມ2 | ≤5E10 ອະຕອມ/ຊມ2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca ແລະ Mn) | |

| ແພັກເກດ | ລາຍລະອຽດການຫຸ້ມຫໍ່ | - | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ຄຳຖາມທີ 1: ຂໍ້ໄດ້ປຽບຫຼັກຂອງການໃຊ້ແຜ່ນ SiC ທຽບກັບແຜ່ນຊິລິໂຄນແບບດັ້ງເດີມໃນເຄື່ອງໃຊ້ໄຟຟ້າແມ່ນຫຍັງ?

ກ1:

ເວເຟີ SiC ມີຂໍ້ໄດ້ປຽບທີ່ສຳຄັນຫຼາຍຢ່າງທຽບກັບເວເຟີຊິລິໂຄນ (Si) ແບບດັ້ງເດີມໃນເອເລັກໂຕຣນິກພະລັງງານ, ລວມທັງ:

ປະສິດທິພາບສູງຂຶ້ນ: SiC ມີແຖບຄວາມຖີ່ກວ້າງກວ່າ (3.26 eV) ເມື່ອທຽບກັບຊິລິກອນ (1.1 eV), ເຊິ່ງຊ່ວຍໃຫ້ອຸປະກອນຕ່າງໆສາມາດເຮັດວຽກໄດ້ໃນແຮງດັນ, ຄວາມຖີ່ ແລະ ອຸນຫະພູມທີ່ສູງຂຶ້ນ. ສິ່ງນີ້ເຮັດໃຫ້ການສູນເສຍພະລັງງານຕ່ຳລົງ ແລະ ປະສິດທິພາບສູງຂຶ້ນໃນລະບົບການປ່ຽນແປງພະລັງງານ.

ການນຳຄວາມຮ້ອນສູງຄວາມນຳຄວາມຮ້ອນຂອງ SiC ສູງກວ່າຊິລິໂຄນຫຼາຍ, ເຊິ່ງເຮັດໃຫ້ການລະບາຍຄວາມຮ້ອນດີຂຶ້ນໃນການນຳໃຊ້ພະລັງງານສູງ, ເຊິ່ງຊ່ວຍປັບປຸງຄວາມໜ້າເຊື່ອຖື ແລະ ອາຍຸການໃຊ້ງານຂອງອຸປະກອນໄຟຟ້າ.

ແຮງດັນໄຟຟ້າ ແລະ ການຈັດການກະແສໄຟຟ້າທີ່ສູງຂຶ້ນອຸປະກອນ SiC ສາມາດຮັບມືກັບລະດັບແຮງດັນ ແລະ ກະແສໄຟຟ້າທີ່ສູງຂຶ້ນ, ເຮັດໃຫ້ພວກມັນເໝາະສົມກັບການນຳໃຊ້ພະລັງງານສູງ ເຊັ່ນ: ພາຫະນະໄຟຟ້າ, ລະບົບພະລັງງານທົດແທນ, ແລະ ລະບົບຂັບເຄື່ອນມໍເຕີອຸດສາຫະກຳ.

ຄວາມໄວໃນການສະຫຼັບທີ່ໄວຂຶ້ນອຸປະກອນ SiC ມີຄວາມສາມາດສະຫຼັບໄດ້ໄວຂຶ້ນ, ເຊິ່ງປະກອບສ່ວນເຂົ້າໃນການຫຼຸດຜ່ອນການສູນເສຍພະລັງງານ ແລະ ຂະໜາດຂອງລະບົບ, ເຮັດໃຫ້ພວກມັນເໝາະສົມສຳລັບການນຳໃຊ້ຄວາມຖີ່ສູງ.

ຄຳຖາມທີ 2: ການນຳໃຊ້ແຜ່ນ SiC ຫຼັກໆໃນອຸດສາຫະກຳລົດຍົນແມ່ນຫຍັງ?

A2:

ໃນອຸດສາຫະກໍາລົດຍົນ, ແຜ່ນຊິລິໂຄນ SiC ຖືກນໍາໃຊ້ຕົ້ນຕໍໃນ:

ລະບົບສົ່ງກຳລັງລົດໄຟຟ້າ (EV)ສ່ວນປະກອບທີ່ອີງໃສ່ SiC ເຊັ່ນອິນເວີເຕີແລະMOSFET ພະລັງງານປັບປຸງປະສິດທິພາບ ແລະ ປະສິດທິພາບຂອງລະບົບສົ່ງກຳລັງຂອງຍານພາຫະນະໄຟຟ້າໂດຍການເຮັດໃຫ້ຄວາມໄວໃນການສະຫຼັບໄວຂຶ້ນ ແລະ ຄວາມໜາແໜ້ນຂອງພະລັງງານສູງຂຶ້ນ. ສິ່ງນີ້ນຳໄປສູ່ອາຍຸການໃຊ້ງານຂອງແບັດເຕີຣີທີ່ຍາວນານຂຶ້ນ ແລະ ປະສິດທິພາບໂດຍລວມຂອງຍານພາຫະນະທີ່ດີຂຶ້ນ.

ເຄື່ອງສາກໄຟໃນຕົວອຸປະກອນ SiC ຊ່ວຍປັບປຸງປະສິດທິພາບຂອງລະບົບສາກໄຟໃນຕົວລົດໂດຍການເຮັດໃຫ້ເວລາສາກໄຟໄວຂຶ້ນ ແລະ ການຈັດການຄວາມຮ້ອນທີ່ດີຂຶ້ນ, ເຊິ່ງເປັນສິ່ງສຳຄັນສຳລັບລົດໄຟຟ້າເພື່ອຮອງຮັບສະຖານີສາກໄຟພະລັງງານສູງ.

ລະບົບການຈັດການແບັດເຕີຣີ (BMS)ເທັກໂນໂລຢີ SiC ຊ່ວຍປັບປຸງປະສິດທິພາບຂອງລະບົບການຈັດການແບັດເຕີຣີ, ເຊິ່ງຊ່ວຍໃຫ້ການຄວບຄຸມແຮງດັນໄຟຟ້າດີຂຶ້ນ, ການຈັດການພະລັງງານທີ່ສູງຂຶ້ນ, ແລະ ອາຍຸການໃຊ້ງານຂອງແບັດເຕີຣີທີ່ຍາວນານຂຶ້ນ.

ຕົວແປງ DC-DC: ເວເຟີ SiC ຖືກນຳໃຊ້ໃນຕົວແປງ DC-DCເພື່ອປ່ຽນພະລັງງານ DC ແຮງດັນສູງໄປເປັນພະລັງງານ DC ແຮງດັນຕ່ຳໃຫ້ມີປະສິດທິພາບຫຼາຍຂຶ້ນ, ເຊິ່ງເປັນສິ່ງສຳຄັນໃນລົດຍົນໄຟຟ້າເພື່ອຈັດການພະລັງງານຈາກແບັດເຕີຣີໄປຫາອົງປະກອບຕ່າງໆໃນລົດ.

ປະສິດທິພາບທີ່ດີເລີດຂອງ SiC ໃນການນຳໃຊ້ແຮງດັນສູງ, ອຸນຫະພູມສູງ ແລະ ປະສິດທິພາບສູງເຮັດໃຫ້ມັນມີຄວາມຈຳເປັນສຳລັບການຫັນປ່ຽນຂອງອຸດສາຫະກຳລົດຍົນໄປສູ່ການເຄື່ອນທີ່ດ້ວຍໄຟຟ້າ.