ເວເຟີ SiC ຂະໜາດ 4 ນິ້ວ 6H ຊັ້ນວັດສະດຸ SiC ເຄິ່ງສນວນ ເປັນຊັ້ນພື້ນຖານ, ຊັ້ນຄົ້ນຄວ້າ ແລະ ຊັ້ນທົດລອງ

ລາຍລະອຽດຜະລິດຕະພັນ

| ຊັ້ນຮຽນ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນຜະລິດມາດຕະຖານ (ຊັ້ນ P) | ຊັ້ນ D (ຊັ້ນ D) | ||||||||

| ເສັ້ນຜ່າສູນກາງ | 99.5 ມມ ~ 100.0 ມມ | ||||||||||

| 4H-SI | 500 ໄມໂຄຣມ ± 20 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | |||||||||

| ທິດທາງຂອງແຜ່ນເວເຟີ |

ນອກແກນ: 4.0° ໄປທາງ < 1120 > ±0.5° ສຳລັບ 4H-N, ໃນແກນ: <0001>±0.5° ສຳລັບ 4H-SI | ||||||||||

| 4H-SI | ≤1 ຊມ-2 | ≤5 ຊມ-2 | ≤15 ຊມ-2 | ||||||||

| 4H-SI | ≥1E9 Ω·ຊມ | ≥1E5 Ω·ຊມ | |||||||||

| ທິດທາງຮາບພຽງຫຼັກ | {10-10} ±5.0° | ||||||||||

| ຄວາມຍາວຮາບພຽງຫຼັກ | 32.5 ມມ ± 2.0 ມມ | ||||||||||

| ຄວາມຍາວຮາບພຽງຂັ້ນສອງ | 18.0 ມມ ± 2.0 ມມ | ||||||||||

| ທິດທາງຮາບພຽງຂັ້ນສອງ | ຊິລິໂຄນຫັນໜ້າຂຶ້ນ: 90° CW. ຈາກມຸມແບນຊັ້ນໜຶ່ງ ±5.0° | ||||||||||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | ||||||||||

| LTV/TTV/Bow /Warp | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| ຄວາມຫຍາບ | ໜ້າຕົວ C | ພາສາໂປໂລຍ | Ra≤1 ນາໂນແມັດ | ||||||||

| ໜ້າສີ | ຊິມພີ | Ra≤0.2 ນາໂນແມັດ | Ra≤0.5 ນາໂນແມັດ | ||||||||

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤ 10 ມມ, ອັນດຽວ ຄວາມຍາວ≤2 ມມ | |||||||||

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.1% | |||||||||

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ພື້ນທີ່ສະສົມ ≤3% | |||||||||

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤3% | |||||||||

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤1 * ເສັ້ນຜ່າສູນກາງແຜ່ນ | |||||||||

| ຊິບຂອບສູງໂດຍຄວາມເຂັ້ມຂອງແສງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥0.2 ມມ | ອະນຸຍາດໃຫ້ 5 ອັນ, ≤1 ມມ ແຕ່ລະອັນ | |||||||||

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ||||||||||

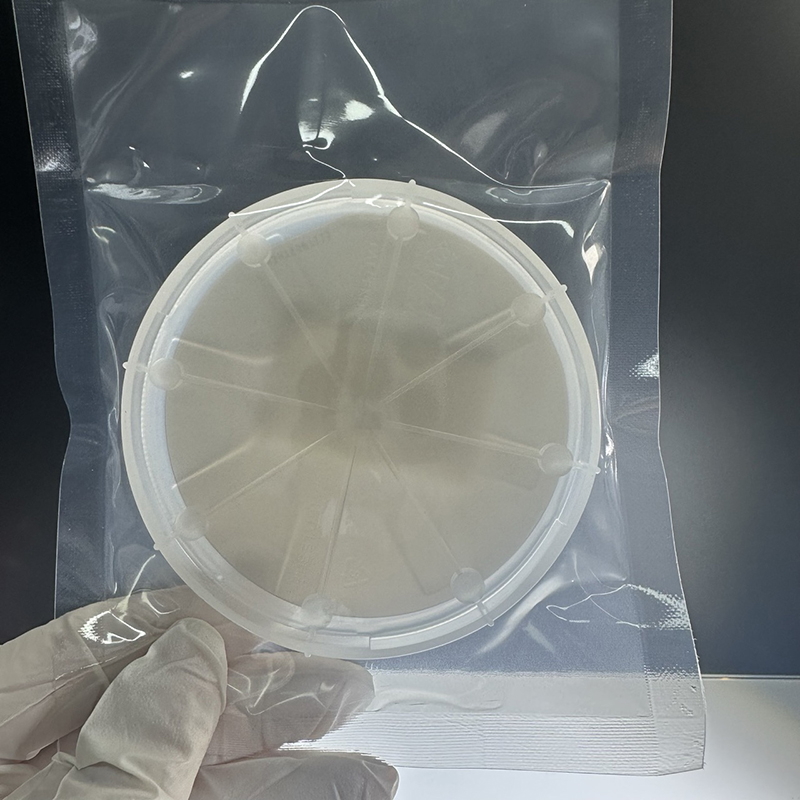

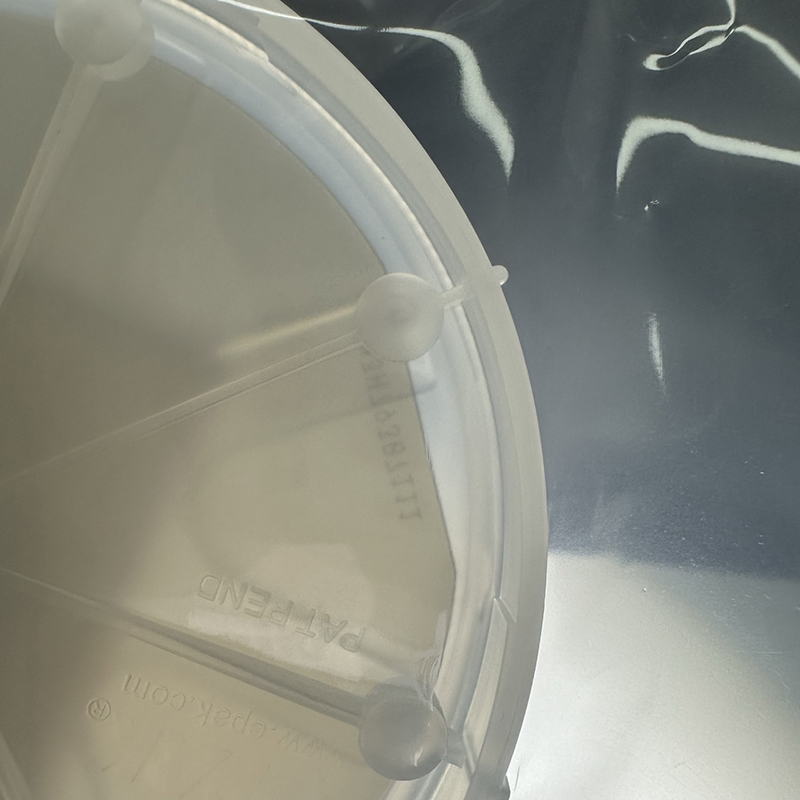

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ||||||||||

ແຜນວາດລະອຽດ

ຜະລິດຕະພັນທີ່ກ່ຽວຂ້ອງ

ຂຽນຂໍ້ຄວາມຂອງທ່ານຢູ່ນີ້ ແລະ ສົ່ງມາໃຫ້ພວກເຮົາ