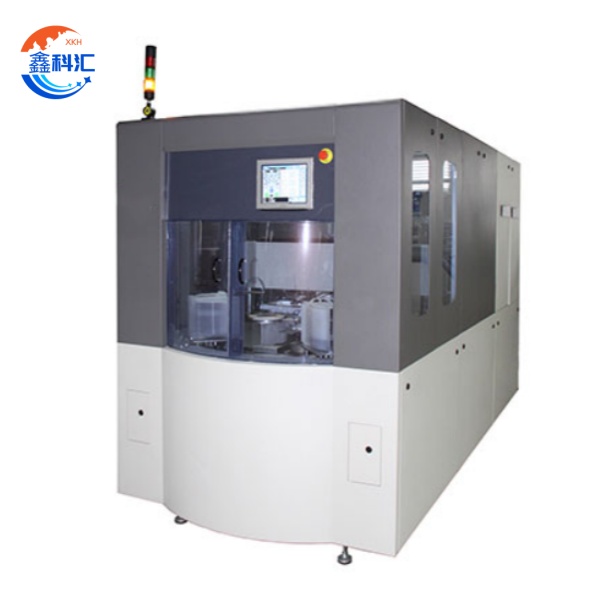

ອຸປະກອນການເຮັດໃຫ້ແຜ່ນເວເຟີບາງລົງສຳລັບການປຸງແຕ່ງແຜ່ນເວເຟີ Sapphire/SiC/Si ຂະໜາດ 4 ນິ້ວ-12 ນິ້ວ

ຫຼັກການເຮັດວຽກ

ຂະບວນການເຮັດໃຫ້ແຜ່ນບາງລົງຂອງແຜ່ນບາງໆດຳເນີນຜ່ານສາມຂັ້ນຕອນຄື:

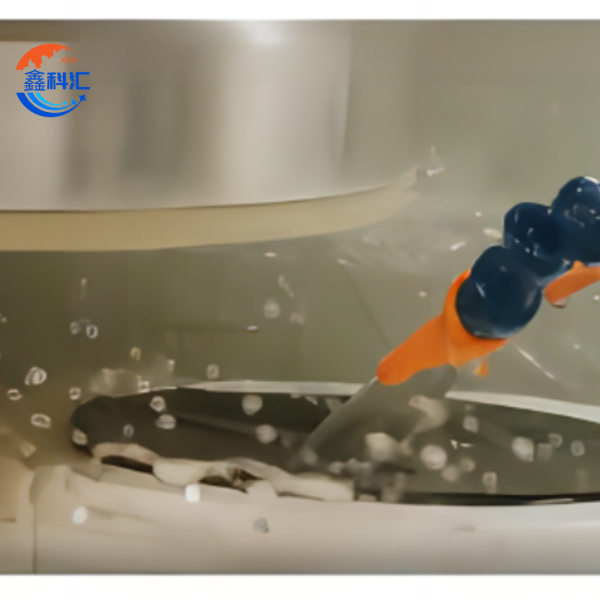

ການບົດຫຍາບ: ລໍ້ເພັດ (ຂະໜາດເມັດພືດ 200–500 μm) ກຳຈັດວັດສະດຸ 50–150 μm ທີ່ 3000–5000 rpm ເພື່ອຫຼຸດຜ່ອນຄວາມໜາຢ່າງໄວວາ.

ການບົດລະອຽດ: ລໍ້ທີ່ລະອຽດກວ່າ (ຂະໜາດເມັດພືດ 1–50 μm) ຫຼຸດຜ່ອນຄວາມໜາລົງເຫຼືອ 20–50 μm ທີ່ <1 μm/s ເພື່ອຫຼຸດຜ່ອນຄວາມເສຍຫາຍໃຕ້ພື້ນຜິວ.

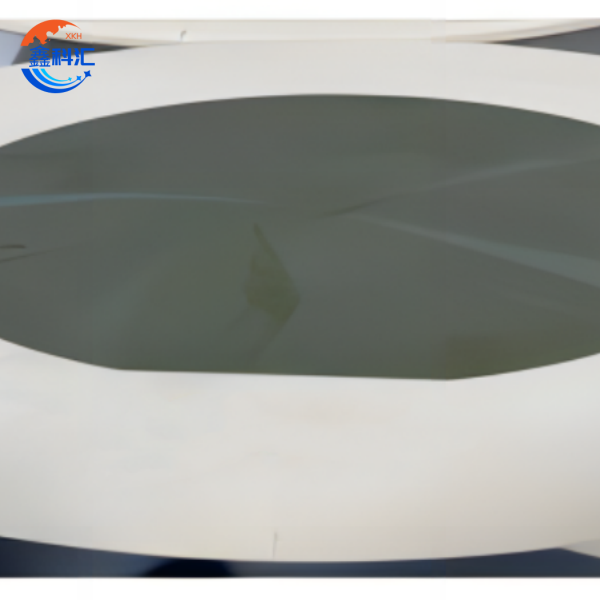

ການຂັດເງົາ (CMP): ນ້ຳຢາເຄມີ-ກົນຈັກຊ່ວຍກຳຈັດຄວາມເສຍຫາຍທີ່ຍັງເຫຼືອ, ບັນລຸ Ra <0.1 nm.

ວັດສະດຸທີ່ເຂົ້າກັນໄດ້

ຊິລິກອນ (Si): ມາດຕະຖານສຳລັບແຜ່ນເວເຟີ CMOS, ບາງລົງເຫຼືອ 25 μm ສຳລັບການວາງຊ້ອນກັນແບບ 3D.

ຊິລິກອນຄາໄບ (SiC): ຕ້ອງການລໍ້ເພັດພິເສດ (ຄວາມເຂັ້ມຂຸ້ນຂອງເພັດ 80%) ເພື່ອຄວາມໝັ້ນຄົງທາງຄວາມຮ້ອນ.

ແກ້ວໄພລິນ (Al₂O₃): ບາງລົງເຖິງ 50 μm ສຳລັບການນຳໃຊ້ UV LED.

ອົງປະກອບຫຼັກຂອງລະບົບ

1. ລະບົບການຂັດ

ເຄື່ອງບົດສອງແກນ: ລວມເອົາການບົດຫຍາບ/ລະອຽດໄວ້ໃນແພລດຟອມດຽວ, ຫຼຸດຜ່ອນເວລາຮອບວຽນລົງ 40%.

Aerostatic Spindle: ຊ່ວງຄວາມໄວ 0–6000 rpm ພ້ອມດ້ວຍການແລ່ນອອກຕາມລັດສະໝີ <0.5 μm.

2. ລະບົບການຈັດການແຜ່ນເວເຟີ

ຫົວຈັບສູນຍາກາດ: ແຮງຍຶດ >50 N ພ້ອມດ້ວຍຄວາມຖືກຕ້ອງຂອງຕຳແໜ່ງ ±0.1 μm.

ແຂນຫຸ່ນຍົນ: ຂົນສົ່ງແຜ່ນເວເຟີຂະໜາດ 4–12 ນິ້ວດ້ວຍຄວາມໄວ 100 ມມ/ວິນາທີ.

3. ລະບົບຄວບຄຸມ

ການແຊກແຊງເລເຊີ: ການຕິດຕາມຄວາມໜາແບບເວລາຈິງ (ຄວາມລະອຽດ 0.01 μm).

AI-Driven Feedforward: ຄາດຄະເນການສວມໃສ່ຂອງລໍ້ ແລະ ປັບພາລາມິເຕີໂດຍອັດຕະໂນມັດ.

4. ການເຮັດຄວາມເຢັນ ແລະ ການທຳຄວາມສະອາດ

ການເຮັດຄວາມສະອາດດ້ວຍຄື້ນສຽງ Ultrasonic: ກຳຈັດອະນຸພາກ >0.5 μm ດ້ວຍປະສິດທິພາບ 99.9%.

ນ້ຳທີ່ບໍ່ມີໄອອອນ: ເຮັດໃຫ້ແຜ່ນເວເຟີເຢັນລົງຕໍ່າກວ່າ 5°C ຈາກສະພາບແວດລ້ອມ.

ຂໍ້ໄດ້ປຽບຫຼັກ

1. ຄວາມແມ່ນຍໍາສູງພິເສດ: TTV (ການປ່ຽນແປງຄວາມໜາທັງໝົດ) <0.5 μm, WTW (ການປ່ຽນແປງຄວາມໜາພາຍໃນແຜ່ນເວເຟີ) <1 μm.

2. ການເຊື່ອມໂຍງຫຼາຍຂະບວນການ: ລວມເອົາການບົດ, CMP, ແລະ ການແກະສະຫຼັກພລາສມາໄວ້ໃນເຄື່ອງດຽວ.

3. ຄວາມເຂົ້າກັນໄດ້ຂອງວັດສະດຸ:

ຊິລິໂຄນ: ການຫຼຸດຜ່ອນຄວາມໜາຈາກ 775 μm ເປັນ 25 μm.

SiC: ບັນລຸ <2 μm TTV ສຳລັບການນຳໃຊ້ RF.

ເວເຟີທີ່ມີສ່ວນປະສົມ: ເວເຟີ InP ທີ່ເສີມດ້ວຍຟອສຟໍຣັດທີ່ມີຄວາມຕ້ານທານຫຼຸດລົງ <5%.

4. ລະບົບອັດຕະໂນມັດອັດສະລິຍະ: ການເຊື່ອມໂຍງ MES ຊ່ວຍຫຼຸດຜ່ອນຄວາມຜິດພາດຂອງມະນຸດໄດ້ 70%.

5. ປະສິດທິພາບດ້ານພະລັງງານ: ການໃຊ້ພະລັງງານຕໍ່າກວ່າ 30% ຜ່ານການເບຣກແບບຟື້ນຟູ.

ແອັບພລິເຄຊັນຫຼັກ

1. ການຫຸ້ມຫໍ່ຂັ້ນສູງ

• ICs 3D: ການເຮັດໃຫ້ແຜ່ນເວເຟີບາງລົງຊ່ວຍໃຫ້ສາມາດວາງຊ້ອນກັນໄດ້ຕາມແນວຕັ້ງຂອງຊິບ logic/ໜ່ວຍຄວາມຈຳ (ເຊັ່ນ: HBM stacks), ເຊິ່ງບັນລຸແບນວິດສູງຂຶ້ນ 10 ເທົ່າ ແລະ ຫຼຸດຜ່ອນການໃຊ້ພະລັງງານລົງ 50% ເມື່ອທຽບກັບໂຊລູຊັ່ນ 2.5D. ອຸປະກອນດັ່ງກ່າວຮອງຮັບການເຊື່ອມຕໍ່ແບບປະສົມ ແລະ ການເຊື່ອມໂຍງ TSV (Through-Silicon Via), ເຊິ່ງສຳຄັນສຳລັບໂປເຊດເຊີ AI/ML ທີ່ຕ້ອງການການເຊື່ອມຕໍ່ pitch <10 μm. ຕົວຢ່າງ, ແຜ່ນເວເຟີຂະໜາດ 12 ນິ້ວທີ່ບາງລົງເຫຼືອ 25 μm ຊ່ວຍໃຫ້ສາມາດວາງຊ້ອນກັນໄດ້ 8+ ຊັ້ນ ໃນຂະນະທີ່ຮັກສາຄວາມບິດເບືອນ <1.5%, ເຊິ່ງສຳຄັນສຳລັບລະບົບ LiDAR ໃນລົດຍົນ.

• ການຫຸ້ມຫໍ່ແບບພັດລົມອອກ: ໂດຍການຫຼຸດຜ່ອນຄວາມໜາຂອງແຜ່ນເວເຟີລົງເຫຼືອ 30 μm, ຄວາມຍາວຂອງການເຊື່ອມຕໍ່ຈະສັ້ນລົງ 50%, ຫຼຸດຜ່ອນຄວາມຊັກຊ້າຂອງສັນຍານ (<0.2 ps/mm) ແລະ ເຮັດໃຫ້ຊິບເລັດບາງພິເສດ 0.4 ມມ ສຳລັບ SoC ມືຖື. ຂະບວນການດັ່ງກ່າວໃຊ້ປະໂຫຍດຈາກຂັ້ນຕອນວິທີການບົດທີ່ຊົດເຊີຍຄວາມກົດດັນເພື່ອປ້ອງກັນການບິດເບືອນ (ການຄວບຄຸມ TTV >50 μm), ຮັບປະກັນຄວາມໜ້າເຊື່ອຖືໃນການນຳໃຊ້ RF ຄວາມຖີ່ສູງ.

2. ເຄື່ອງໃຊ້ໄຟຟ້າ

• ໂມດູນ IGBT: ການເຮັດໃຫ້ບາງລົງເຖິງ 50 μm ຊ່ວຍຫຼຸດຜ່ອນຄວາມຕ້ານທານຄວາມຮ້ອນໃຫ້ເຫຼືອ <0.5°C/W, ເຮັດໃຫ້ MOSFETs SiC 1200V ສາມາດເຮັດວຽກໄດ້ທີ່ອຸນຫະພູມຈຸດເຊື່ອມຕໍ່ 200°C. ອຸປະກອນຂອງພວກເຮົາໃຊ້ການບົດຫຼາຍຂັ້ນຕອນ (ຫຍາບ: ລະອຽດ 46 μm → ລະອຽດ: ລະອຽດ 4 μm) ເພື່ອລົບລ້າງຄວາມເສຍຫາຍໃຕ້ດິນ, ບັນລຸຄວາມໜ້າເຊື່ອຖືຂອງວົງຈອນຄວາມຮ້ອນຫຼາຍກວ່າ 10,000 ຮອບວຽນ. ນີ້ແມ່ນສິ່ງສຳຄັນສຳລັບອິນເວີເຕີ EV, ບ່ອນທີ່ແຜ່ນ SiC ໜາ 10 μm ປັບປຸງຄວາມໄວໃນການສະຫຼັບໄດ້ 30%.

• ອຸປະກອນພະລັງງານ GaN-on-SiC: ການຫຼຸດຄວາມບາງຂອງແຜ່ນເວເຟີລົງເຖິງ 80 μm ຊ່ວຍເພີ່ມການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນ (μ > 2000 cm²/V·s) ສຳລັບ 650V GaN HEMTs, ຫຼຸດຜ່ອນການສູນເສຍການນຳໄຟຟ້າລົງ 18%. ຂະບວນການດັ່ງກ່າວໃຊ້ການເຈາະດ້ວຍເລເຊີເພື່ອປ້ອງກັນການແຕກໃນລະຫວ່າງການຫຼຸດຄວາມບາງ, ບັນລຸການບิ่นຂອບ <5 μm ສຳລັບເຄື່ອງຂະຫຍາຍສຽງ RF.

3. ອອບໂຕອີເລັກໂທຣນິກ

• ໄຟ LED GaN-on-SiC: ຊັ້ນຮອງພື້ນ sapphire 50 μm ຊ່ວຍປັບປຸງປະສິດທິພາບການສະກັດແສງ (LEE) ເປັນ 85% (ທຽບກັບ 65% ສຳລັບເວເຟີ 150 μm) ໂດຍການຫຼຸດຜ່ອນການດັກຈັບໂຟຕອນ. ການຄວບຄຸມ TTV ຕ່ຳຫຼາຍ (<0.3 μm) ຂອງອຸປະກອນຂອງພວກເຮົາຮັບປະກັນການປ່ອຍແສງ LED ຢ່າງເປັນເອກະພາບໃນທົ່ວເວເຟີຂະໜາດ 12 ນິ້ວ, ເຊິ່ງສຳຄັນສຳລັບຈໍສະແດງຜົນ Micro-LED ທີ່ຕ້ອງການຄວາມສະເໝີພາບຂອງຄວາມຍາວຄື້ນ <100nm.

• ຊິລິກອນໂຟໂຕນິກ: ເວເຟີຊິລິກອນໜາ 25μm ຊ່ວຍໃຫ້ການສູນເສຍການແຜ່ກະຈາຍໃນຄື້ນນຳທາງຫຼຸດລົງ 3 dB/cm, ເຊິ່ງຈຳເປັນສຳລັບເຄື່ອງຮັບສົ່ງສັນຍານແສງ 1.6 Tbps. ຂະບວນການດັ່ງກ່າວປະສົມປະສານການເຮັດໃຫ້ລຽບ CMP ເພື່ອຫຼຸດຜ່ອນຄວາມຫຍາບຂອງພື້ນຜິວໃຫ້ Ra <0.1 nm, ເພີ່ມປະສິດທິພາບການເຊື່ອມຕໍ່ໄດ້ 40%.

4. ເຊັນເຊີ MEMS

• ເຄື່ອງວັດຄວາມເລັ່ງ: ເວເຟີຊິລິໂຄນ 25 μm ບັນລຸ SNR >85 dB (ທຽບກັບ 75 dB ສຳລັບເວເຟີ 50 μm) ໂດຍການເພີ່ມຄວາມອ່ອນໄຫວຕໍ່ການຍ້າຍມວນສານທີ່ພິສູດໄດ້. ລະບົບການບົດສອງແກນຂອງພວກເຮົາຊົດເຊີຍການປ່ຽນແປງຄວາມຕຶງຄຽດ, ຮັບປະກັນການເລື່ອນຄວາມອ່ອນໄຫວ <0.5% ໃນໄລຍະ -40°C ຫາ 125°C. ການນຳໃຊ້ລວມມີການກວດຈັບການອຸບັດຕິເຫດຂອງລົດຍົນ ແລະ ການຕິດຕາມການເຄື່ອນໄຫວ AR/VR.

• ເຊັນເຊີຄວາມດັນ: ການເຮັດໃຫ້ບາງລົງເຖິງ 40 μm ຊ່ວຍໃຫ້ມີລະດັບການວັດແທກ 0–300 ບາ ດ້ວຍ hysteresis FS <0.1%. ໂດຍການໃຊ້ການຜູກມັດຊົ່ວຄາວ (ຕົວຮອງຮັບແກ້ວ), ຂະບວນການດັ່ງກ່າວຫຼີກລ່ຽງການແຕກຫັກຂອງແຜ່ນ wafer ໃນລະຫວ່າງການແກະສະຫຼັກດ້ານຫຼັງ, ເຊິ່ງບັນລຸຄວາມທົນທານຕໍ່ຄວາມດັນເກີນ <1 μm ສຳລັບເຊັນເຊີ IoT ອຸດສາຫະກຳ.

• ການຮ່ວມມືດ້ານວິຊາການ: ອຸປະກອນການເຮັດໃຫ້ບາງແຜ່ນເວເຟີຂອງພວກເຮົາລວມເອົາການບົດແບບກົນຈັກ, CMP, ແລະ ການແກະສະຫຼັກດ້ວຍພລາສມາເພື່ອແກ້ໄຂບັນຫາວັດສະດຸທີ່ຫຼາກຫຼາຍ (Si, SiC, Sapphire). ຕົວຢ່າງ, GaN-on-SiC ຕ້ອງການການບົດແບບປະສົມ (ລໍ້ເພັດ + ພລາສມາ) ເພື່ອດຸ່ນດ່ຽງຄວາມແຂງ ແລະ ການຂະຫຍາຍຕົວທາງຄວາມຮ້ອນ, ໃນຂະນະທີ່ເຊັນເຊີ MEMS ຮຽກຮ້ອງໃຫ້ມີຄວາມຫຍາບຂອງພື້ນຜິວຕ່ຳກວ່າ 5 nm ຜ່ານການຂັດ CMP.

• ຜົນກະທົບຂອງອຸດສາຫະກໍາ: ໂດຍການເຮັດໃຫ້ເວເຟີທີ່ບາງກວ່າ ແລະ ມີປະສິດທິພາບສູງກວ່າ, ເທັກໂນໂລຢີນີ້ຊຸກຍູ້ນະວັດຕະກໍາໃນຊິບ AI, ໂມດູນ 5G mmWave, ແລະ ອຸປະກອນເອເລັກໂຕຣນິກທີ່ມີຄວາມຍືດຫຍຸ່ນ, ດ້ວຍຄວາມທົນທານຂອງ TTV <0.1 μm ສໍາລັບຈໍສະແດງຜົນແບບພັບໄດ້ ແລະ <0.5 μm ສໍາລັບເຊັນເຊີ LiDAR ລົດຍົນ.

ການບໍລິການຂອງ XKH

1. ວິທີແກ້ໄຂທີ່ກຳນົດເອງ

ການຕັ້ງຄ່າທີ່ສາມາດຂະຫຍາຍໄດ້: ການອອກແບບຫ້ອງຂະໜາດ 4–12 ນິ້ວພ້ອມດ້ວຍການໂຫຼດ/ຍົກອັດຕະໂນມັດ.

ການສະໜັບສະໜູນການໃຊ້ສານເສີມ: ສູດອາຫານທີ່ກຳນົດເອງສຳລັບຜລຶກທີ່ມີສານເສີມ Er/Yb ແລະ ເວເຟີ InP/GaAs.

2. ການສະໜັບສະໜູນແບບຄົບວົງຈອນ

ການພັດທະນາຂະບວນການ: ການທົດລອງໃຊ້ຟຣີແລ່ນພ້ອມກັບການເພີ່ມປະສິດທິພາບ.

ການຝຶກອົບຮົມທົ່ວໂລກ: ກອງປະຊຸມດ້ານວິຊາການປະຈຳປີກ່ຽວກັບການບຳລຸງຮັກສາ ແລະ ການແກ້ໄຂບັນຫາ.

3. ການປຸງແຕ່ງຫຼາຍວັດສະດຸ

SiC: ແຜ່ນເວເຟີບາງລົງເຖິງ 100 μm ດ້ວຍ Ra < 0.1 nm.

Sapphire: ຄວາມໜາ 50μm ສຳລັບປ່ອງຢ້ຽມເລເຊີ UV (ການສົ່ງຜ່ານ >92%@200 nm).

4. ການບໍລິການທີ່ມີມູນຄ່າເພີ່ມ

ການສະໜອງສິນຄ້າບໍລິໂພກ: ລໍ້ເພັດ (2000+ ແຜ່ນ/ຊີວິດ) ແລະ ຂີ້ເທົ່າ CMP.

ສະຫຼຸບ

ອຸປະກອນການບາງແຜ່ນເວເຟີນີ້ໃຫ້ຄວາມແມ່ນຍໍາຊັ້ນນໍາຂອງອຸດສາຫະກໍາ, ຄວາມຄ່ອງແຄ້ວຫຼາຍວັດສະດຸ, ແລະ ລະບົບອັດຕະໂນມັດອັດສະລິຍະ, ເຮັດໃຫ້ມັນເປັນສິ່ງທີ່ຂາດບໍ່ໄດ້ສໍາລັບການເຊື່ອມໂຍງ 3D ແລະ ເຄື່ອງໃຊ້ໄຟຟ້າພະລັງງານ. ການບໍລິການທີ່ຄົບຖ້ວນຂອງ XKH - ຕັ້ງແຕ່ການປັບແຕ່ງຈົນເຖິງການປະມວນຜົນຫຼັງການປຸງແຕ່ງ - ຮັບປະກັນວ່າລູກຄ້າບັນລຸປະສິດທິພາບດ້ານຄ່າໃຊ້ຈ່າຍ ແລະ ຄວາມເປັນເລີດດ້ານປະສິດທິພາບໃນການຜະລິດເຄິ່ງຕົວນໍາ.