ໃນຖານະເປັນວັດສະດຸຊັ້ນຮອງຂອງເຊມິຄອນດັກເຕີລຸ້ນທີສາມ,ຊິລິກອນຄາໄບ (SiC)ຜລຶກດຽວມີທ່າແຮງໃນການນຳໃຊ້ຢ່າງກວ້າງຂວາງໃນການຜະລິດອຸປະກອນເອເລັກໂຕຣນິກຄວາມຖີ່ສູງ ແລະ ພະລັງງານສູງ. ເຕັກໂນໂລຊີການປຸງແຕ່ງຂອງ SiC ມີບົດບາດສຳຄັນໃນການຜະລິດວັດສະດຸພື້ນຖານທີ່ມີຄຸນນະພາບສູງ. ບົດຄວາມນີ້ແນະນຳສະພາບການຄົ້ນຄວ້າໃນປະຈຸບັນກ່ຽວກັບເຕັກໂນໂລຊີການປຸງແຕ່ງ SiC ທັງໃນປະເທດຈີນ ແລະ ຕ່າງປະເທດ, ການວິເຄາະ ແລະ ປຽບທຽບກົນໄກຂອງຂະບວນການຕັດ, ບົດ, ແລະ ຂັດ, ພ້ອມທັງແນວໂນ້ມໃນຄວາມຮາບພຽງຂອງແຜ່ນເວເຟີ ແລະ ຄວາມຫຍາບຂອງພື້ນຜິວ. ມັນຍັງຊີ້ໃຫ້ເຫັນເຖິງສິ່ງທ້າທາຍທີ່ມີຢູ່ໃນການປຸງແຕ່ງແຜ່ນເວເຟີ SiC ແລະ ປຶກສາຫາລືກ່ຽວກັບທິດທາງການພັດທະນາໃນອະນາຄົດ.

ຊິລິກອນຄາໄບ (SiC)ເວເຟີເປັນວັດສະດຸພື້ນຖານທີ່ສຳຄັນສຳລັບອຸປະກອນເຄິ່ງຕົວນຳລຸ້ນທີສາມ ແລະ ມີຄວາມສຳຄັນ ແລະ ມີທ່າແຮງທາງການຕະຫຼາດຢ່າງຫຼວງຫຼາຍໃນຂົງເຂດຕ່າງໆເຊັ່ນ: ໄມໂຄຣອີເລັກໂທຣນິກ, ເອເລັກໂຕຣນິກພະລັງງານ, ແລະ ໄຟເຄິ່ງຕົວນຳ. ເນື່ອງຈາກຄວາມແຂງ ແລະ ຄວາມໝັ້ນຄົງທາງເຄມີທີ່ສູງຫຼາຍຂອງຜລຶກ SiC ດ່ຽວ, ວິທີການປະມວນຜົນແບບເຄິ່ງຕົວນຳແບບດັ້ງເດີມບໍ່ເໝາະສົມກັບເຄື່ອງຈັກຂອງມັນທັງໝົດ. ເຖິງແມ່ນວ່າບໍລິສັດສາກົນຫຼາຍແຫ່ງໄດ້ດຳເນີນການຄົ້ນຄວ້າຢ່າງກວ້າງຂວາງກ່ຽວກັບການປະມວນຜົນຂອງຜລຶກດ່ຽວ SiC ທີ່ຕ້ອງການເຕັກນິກສູງ, ແຕ່ເຕັກໂນໂລຢີທີ່ກ່ຽວຂ້ອງແມ່ນຖືກຮັກສາເປັນຄວາມລັບຢ່າງເຂັ້ມງວດ.

ໃນຊຸມປີມໍ່ໆມານີ້, ຈີນໄດ້ເພີ່ມຄວາມພະຍາຍາມໃນການພັດທະນາວັດສະດຸ ແລະ ອຸປະກອນ SiC ທີ່ເປັນຜລຶກດ່ຽວ. ເຖິງຢ່າງໃດກໍ່ຕາມ, ຄວາມກ້າວໜ້າຂອງເຕັກໂນໂລຊີອຸປະກອນ SiC ໃນປະເທດໃນປະຈຸບັນແມ່ນມີຂໍ້ຈຳກັດຍ້ອນຂໍ້ຈຳກັດໃນເຕັກໂນໂລຊີການປຸງແຕ່ງ ແລະ ຄຸນນະພາບຂອງແຜ່ນແພ. ດັ່ງນັ້ນ, ມັນຈຶ່ງເປັນສິ່ງຈຳເປັນສຳລັບຈີນທີ່ຈະປັບປຸງຄວາມສາມາດໃນການປຸງແຕ່ງ SiC ເພື່ອເສີມຂະຫຍາຍຄຸນນະພາບຂອງຊັ້ນຮອງຜລຶກດ່ຽວ SiC ແລະ ບັນລຸການນຳໃຊ້ຕົວຈິງ ແລະ ການຜະລິດເປັນຈຳນວນຫຼວງຫຼາຍ.

ຂັ້ນຕອນການປຸງແຕ່ງຫຼັກປະກອບມີ: ການຕັດ → ການບົດຫຍາບ → ການບົດລະອຽດ → ການຂັດຫຍາບ (ການຂັດກົນຈັກ) → ການຂັດລະອຽດ (ການຂັດກົນຈັກທາງເຄມີ, CMP) → ການກວດກາ.

| ຂັ້ນຕອນ | ການປຸງແຕ່ງແຜ່ນເວເຟີ SiC | ການປຸງແຕ່ງວັດສະດຸຜລຶກດຽວແບບເຊມິຄອນດັກເຕີແບບດັ້ງເດີມ |

| ການຕັດ | ໃຊ້ເທັກໂນໂລຢີເລື່ອຍຫຼາຍສາຍເພື່ອຕັດໂລຫະ SiC ໃຫ້ເປັນແຜ່ນບາງໆ | ໂດຍປົກກະຕິແລ້ວໃຊ້ເຕັກນິກການຕັດໃບມີດທີ່ມີເສັ້ນຜ່າສູນກາງດ້ານໃນ ຫຼື ເສັ້ນຜ່າສູນກາງດ້ານນອກ |

| ການບົດ | ແບ່ງອອກເປັນບົດຫຍາບ ແລະ ບົດລະອຽດ ເພື່ອກຳຈັດຮອຍເລື່ອຍ ແລະ ຊັ້ນຄວາມເສຍຫາຍທີ່ເກີດຈາກການຕັດ | ວິທີການຂັດອາດແຕກຕ່າງກັນ, ແຕ່ເປົ້າໝາຍແມ່ນຄືກັນ |

| ການຂັດເງົາ | ລວມທັງການຂັດເງົາແບບຫຍາບ ແລະ ຄວາມແມ່ນຍໍາສູງໂດຍໃຊ້ການຂັດເງົາແບບກົນຈັກ ແລະ ເຄມີ (CMP) | ໂດຍປົກກະຕິແລ້ວຈະປະກອບມີການຂັດເງົາທາງເຄມີ (CMP), ເຖິງແມ່ນວ່າຂັ້ນຕອນສະເພາະອາດແຕກຕ່າງກັນ |

ການຕັດຜລຶກ SiC ດ່ຽວ

ໃນການປະມວນຜົນຂອງຜລຶກ SiC ດ່ຽວ, ການຕັດແມ່ນຂັ້ນຕອນທຳອິດ ແລະ ມີຄວາມສຳຄັນຫຼາຍ. ການປ່ຽນແປງຂອງໂຄ້ງ, ບິດງໍ, ແລະ ຄວາມໜາທັງໝົດ (TTV) ຂອງແຜ່ນເວເຟີ ທີ່ເປັນຜົນມາຈາກຂະບວນການຕັດ ກຳນົດຄຸນນະພາບ ແລະ ປະສິດທິພາບຂອງການບົດ ແລະ ການຂັດເງົາຕໍ່ມາ.

ເຄື່ອງມືຕັດສາມາດຈັດປະເພດຕາມຮູບຮ່າງໄດ້ເປັນເລື່ອຍຕັດຮູບເພັດທີ່ມີເສັ້ນຜ່າສູນກາງດ້ານໃນ (ID), ເລື່ອຍຕັດຮູບເສັ້ນຜ່າສູນກາງດ້ານນອກ (OD), ເລື່ອຍຕັດແຖບ, ແລະ ເລື່ອຍຕັດລວດ. ເລື່ອຍຕັດລວດສາມາດຈັດປະເພດຕາມປະເພດການເຄື່ອນໄຫວຂອງມັນໄດ້ເປັນລະບົບລວດແບບກັບ ແລະ ແບບວົງ (ບໍ່ມີທີ່ສິ້ນສຸດ). ອີງຕາມກົນໄກການຕັດຂອງເຄື່ອງຂັດ, ເຕັກນິກການຕັດດ້ວຍເລື່ອຍຕັດລວດສາມາດແບ່ງອອກເປັນສອງປະເພດຄື: ການເລື່ອຍຕັດລວດແບບອິດສະຫຼະ ແລະ ການເລື່ອຍຕັດລວດເພັດແບບຄົງທີ່.

1.1 ວິທີການຕັດແບບດັ້ງເດີມ

ຄວາມເລິກຂອງການຕັດຂອງເລື່ອຍທີ່ມີເສັ້ນຜ່າສູນກາງພາຍນອກ (OD) ແມ່ນຖືກຈຳກັດໂດຍເສັ້ນຜ່າສູນກາງຂອງໃບມີດ. ໃນລະຫວ່າງຂະບວນການຕັດ, ໃບມີດມັກຈະມີການສັ່ນສະເທືອນ ແລະ ການບິດເບືອນ, ເຊິ່ງເຮັດໃຫ້ເກີດລະດັບສຽງດັງສູງ ແລະ ຄວາມແຂງກະດ້າງທີ່ບໍ່ດີ. ເລື່ອຍທີ່ມີເສັ້ນຜ່າສູນກາງພາຍໃນ (ID) ໃຊ້ສານຂັດເພັດຢູ່ເສັ້ນຮອບວົງພາຍໃນຂອງໃບມີດເປັນຂອບຕັດ. ໃບມີດເຫຼົ່ານີ້ສາມາດບາງໄດ້ເຖິງ 0.2 ມມ. ໃນລະຫວ່າງການຕັດ, ໃບມີດ ID ຈະໝຸນດ້ວຍຄວາມໄວສູງ ໃນຂະນະທີ່ວັດສະດຸທີ່ຈະຕັດເຄື່ອນທີ່ຕາມລັດສະໝີທຽບກັບຈຸດໃຈກາງຂອງໃບມີດ, ເຮັດໃຫ້ການຕັດຜ່ານການເຄື່ອນທີ່ທີ່ກ່ຽວຂ້ອງນີ້.

ເລື່ອຍຕັດແບບວົງແຫວນເພັດຕ້ອງການການຢຸດ ແລະ ການປີ້ນກັບເລື້ອຍໆ, ແລະ ຄວາມໄວໃນການຕັດແມ່ນຕໍ່າຫຼາຍ - ໂດຍປົກກະຕິແລ້ວບໍ່ເກີນ 2 ແມັດ/ວິນາທີ. ພວກມັນຍັງປະສົບກັບການສວມໃສ່ທາງກົນຈັກທີ່ສຳຄັນ ແລະ ຄ່າໃຊ້ຈ່າຍໃນການບຳລຸງຮັກສາສູງ. ເນື່ອງຈາກຄວາມກວ້າງຂອງໃບເລື່ອຍ, ລັດສະໝີການຕັດບໍ່ສາມາດນ້ອຍເກີນໄປ, ແລະ ການຕັດຫຼາຍແຜ່ນກໍ່ເປັນໄປບໍ່ໄດ້. ເຄື່ອງມືເລື່ອຍແບບດັ້ງເດີມເຫຼົ່ານີ້ຖືກຈຳກັດໂດຍຄວາມແຂງແກ່ນຂອງຖານ ແລະ ບໍ່ສາມາດຕັດໂຄ້ງ ຫຼື ມີລັດສະໝີການໝຸນທີ່ຈຳກັດ. ພວກມັນມີຄວາມສາມາດໃນການຕັດຊື່ເທົ່ານັ້ນ, ຜະລິດຮອຍແຕກກວ້າງ, ມີອັດຕາຜົນຜະລິດຕໍ່າ, ແລະ ດັ່ງນັ້ນຈຶ່ງບໍ່ເໝາະສົມສຳລັບການຕັດ.ຜລຶກ SiC.

1.2 ເຄື່ອງຕັດລວດແບບບໍ່ມີສາຍຟຣີ ການຕັດຫຼາຍລວດ

ເຕັກນິກການຕັດດ້ວຍເລື່ອຍລວດແບບຂັດຟຣີໃຊ້ການເຄື່ອນໄຫວຢ່າງໄວວາຂອງລວດເພື່ອນຳເອົານ້ຳຢາງເຂົ້າໄປໃນ kerf, ເຮັດໃຫ້ສາມາດກຳຈັດວັດສະດຸໄດ້. ມັນໃຊ້ໂຄງສ້າງແບບກັບໄປກັບມາ ແລະ ປະຈຸບັນເປັນວິທີການທີ່ພັດທະນາແລ້ວ ແລະ ນຳໃຊ້ຢ່າງກວ້າງຂວາງສຳລັບການຕັດຫຼາຍແຜ່ນທີ່ມີປະສິດທິພາບຂອງຊິລິໂຄນຜລຶກດຽວ. ຢ່າງໃດກໍຕາມ, ການນຳໃຊ້ຂອງມັນໃນການຕັດ SiC ຍັງບໍ່ທັນໄດ້ຮັບການສຶກສາຢ່າງກວ້າງຂວາງເທື່ອ.

ເລື່ອຍລວດຂັດສາມາດປຸງແຕ່ງແຜ່ນເວເຟີທີ່ມີຄວາມໜາໜ້ອຍກວ່າ 300 μm. ພວກມັນໃຫ້ການສູນເສຍ kerf ຕ່ຳ, ບໍ່ຄ່ອຍເຮັດໃຫ້ເກີດການບิ่น, ແລະ ເຮັດໃຫ້ມີຄຸນນະພາບພື້ນຜິວທີ່ດີພໍສົມຄວນ. ຢ່າງໃດກໍຕາມ, ເນື່ອງຈາກກົນໄກການກຳຈັດວັດສະດຸ - ໂດຍອີງໃສ່ການມ້ວນ ແລະ ການເປັນຮອຍແຫວ່ງຂອງວັດສະດຸຂັດ - ພື້ນຜິວແຜ່ນເວເຟີມັກຈະພັດທະນາຄວາມກົດດັນທີ່ເຫຼືອຢ່າງຫຼວງຫຼາຍ, ຮອຍແຕກຂະໜາດນ້ອຍ, ແລະ ຊັ້ນຄວາມເສຍຫາຍທີ່ເລິກກວ່າ. ສິ່ງນີ້ນຳໄປສູ່ການບິດເບືອນແຜ່ນເວເຟີ, ເຮັດໃຫ້ມັນຍາກທີ່ຈະຄວບຄຸມຄວາມຖືກຕ້ອງຂອງໂປຣໄຟລ໌ພື້ນຜິວ, ແລະ ເພີ່ມພາລະໃນຂັ້ນຕອນການປຸງແຕ່ງຕໍ່ໄປ.

ປະສິດທິພາບການຕັດແມ່ນໄດ້ຮັບອິດທິພົນຢ່າງຫຼວງຫຼາຍຈາກນ້ຳຢາຂັດ; ມັນຈຳເປັນຕ້ອງຮັກສາຄວາມຄົມຊັດຂອງນ້ຳຢາຂັດ ແລະ ຄວາມເຂັ້ມຂຸ້ນຂອງນ້ຳຢາຂັດ. ການບຳບັດ ແລະ ການຣີໄຊເຄີນນ້ຳຢາຂັດແມ່ນມີລາຄາແພງ. ເມື່ອຕັດໂລຫະຂະໜາດໃຫຍ່, ນ້ຳຢາຂັດມີຄວາມຫຍຸ້ງຍາກໃນການເຈາະເຂົ້າໄປໃນ kerfs ເລິກ ແລະ ຍາວ. ພາຍໃຕ້ຂະໜາດເມັດຂັດດຽວກັນ, ການສູນເສຍ kerf ແມ່ນສູງກວ່າເລື່ອຍລວດຂັດຄົງທີ່.

1.3 ເລື່ອຍຕັດເສັ້ນລວດເພັດແບບຂັດຄົງທີ່ດ້ວຍຫຼາຍສາຍ

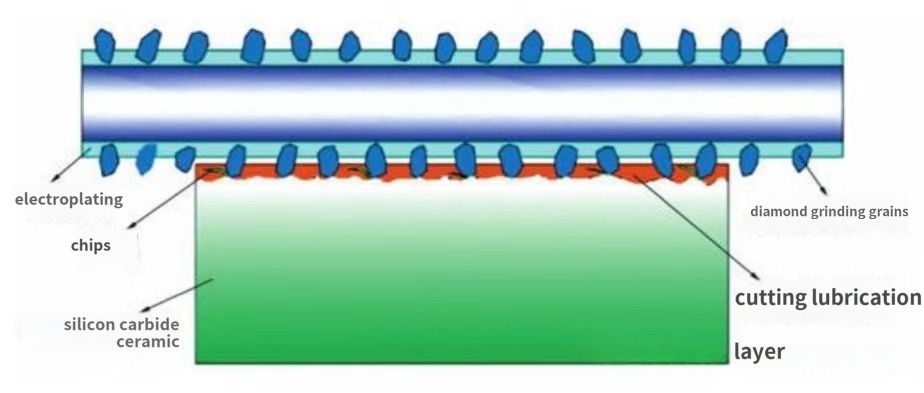

ເລື່ອຍຕັດລວດເພັດທີ່ມີການຂັດຄົງທີ່ໂດຍທົ່ວໄປແລ້ວແມ່ນເຮັດໂດຍການຝັງອະນຸພາກເພັດໃສ່ຊັ້ນຮອງລວດເຫຼັກໂດຍຜ່ານວິທີການເຄືອບດ້ວຍໄຟຟ້າ, ການເຜົາ, ຫຼື ການຜູກມັດດ້ວຍຢາງ. ເລື່ອຍຕັດລວດເພັດທີ່ມີການເຄືອບດ້ວຍໄຟຟ້າມີຂໍ້ດີຕ່າງໆເຊັ່ນ: ຮອຍຕັດແຄບກວ່າ, ຄຸນນະພາບການຊອຍທີ່ດີກວ່າ, ປະສິດທິພາບສູງກວ່າ, ການປົນເປື້ອນຕ່ຳກວ່າ, ແລະ ຄວາມສາມາດໃນການຕັດວັດສະດຸທີ່ມີຄວາມແຂງສູງ.

ເຄື່ອງເລື່ອຍລວດເພັດທີ່ເຄືອບດ້ວຍໄຟຟ້າແບບຕ່ອງໂສ້ແມ່ນວິທີການຕັດ SiC ທີ່ນິຍົມໃຊ້ກັນຢ່າງກວ້າງຂວາງທີ່ສຸດໃນປະຈຸບັນ. ຮູບທີ 1 (ບໍ່ໄດ້ສະແດງຢູ່ນີ້) ສະແດງໃຫ້ເຫັນເຖິງຄວາມຮາບພຽງຂອງພື້ນຜິວຂອງແຜ່ນ SiC ທີ່ຕັດໂດຍໃຊ້ເຕັກນິກນີ້. ເມື່ອການຕັດດຳເນີນໄປ, ການບິດງໍຂອງແຜ່ນຈະເພີ່ມຂຶ້ນ. ນີ້ແມ່ນຍ້ອນວ່າພື້ນທີ່ສຳຜັດລະຫວ່າງລວດແລະວັດສະດຸຈະເພີ່ມຂຶ້ນເມື່ອລວດເຄື່ອນລົງ, ເຊິ່ງເຮັດໃຫ້ຄວາມຕ້ານທານແລະການສັ່ນສະເທືອນຂອງລວດເພີ່ມຂຶ້ນ. ເມື່ອລວດຮອດເສັ້ນຜ່າສູນກາງສູງສຸດຂອງແຜ່ນ, ການສັ່ນສະເທືອນຈະຢູ່ທີ່ຈຸດສູງສຸດ, ເຊິ່ງສົ່ງຜົນໃຫ້ມີການບິດງໍສູງສຸດ.

ໃນໄລຍະຕໍ່ມາຂອງການຕັດ, ເນື່ອງຈາກສາຍໄຟໄດ້ຮັບການເລັ່ງ, ການເຄື່ອນໄຫວດ້ວຍຄວາມໄວທີ່ໝັ້ນຄົງ, ການຊະລໍຕົວ, ການຢຸດ, ແລະ ການປີ້ນກັບ, ພ້ອມກັບຄວາມຫຍຸ້ງຍາກໃນການກຳຈັດສິ່ງເສດເຫຼືອທີ່ມີນ້ຳຢາຫຼໍ່ເຢັນ, ຄຸນນະພາບພື້ນຜິວຂອງແຜ່ນແພຈະຊຸດໂຊມລົງ. ການປີ້ນກັບຂອງສາຍໄຟ ແລະ ການປ່ຽນແປງຂອງຄວາມໄວ, ເຊັ່ນດຽວກັນກັບອະນຸພາກເພັດຂະໜາດໃຫຍ່ຢູ່ເທິງສາຍໄຟ, ແມ່ນສາເຫດຕົ້ນຕໍຂອງຮອຍຂີດຂ່ວນພື້ນຜິວ.

1.4 ເຕັກໂນໂລຊີການແຍກຄວາມເຢັນ

ການແຍກຜລຶກ SiC ດ່ຽວແບບເຢັນເປັນຂະບວນການທີ່ມີນະວັດຕະກໍາໃນຂົງເຂດການປຸງແຕ່ງວັດສະດຸເຄິ່ງຕົວນໍາລຸ້ນທີສາມ. ໃນຊຸມປີມໍ່ໆມານີ້, ມັນໄດ້ຮັບຄວາມສົນໃຈຢ່າງຫຼວງຫຼາຍເນື່ອງຈາກຂໍ້ໄດ້ປຽບທີ່ໂດດເດັ່ນໃນການປັບປຸງຜົນຜະລິດແລະການຫຼຸດຜ່ອນການສູນເສຍວັດສະດຸ. ເຕັກໂນໂລຢີສາມາດວິເຄາະໄດ້ຈາກສາມດ້ານຄື: ຫຼັກການເຮັດວຽກ, ຂະບວນການ, ແລະຂໍ້ໄດ້ປຽບຫຼັກ.

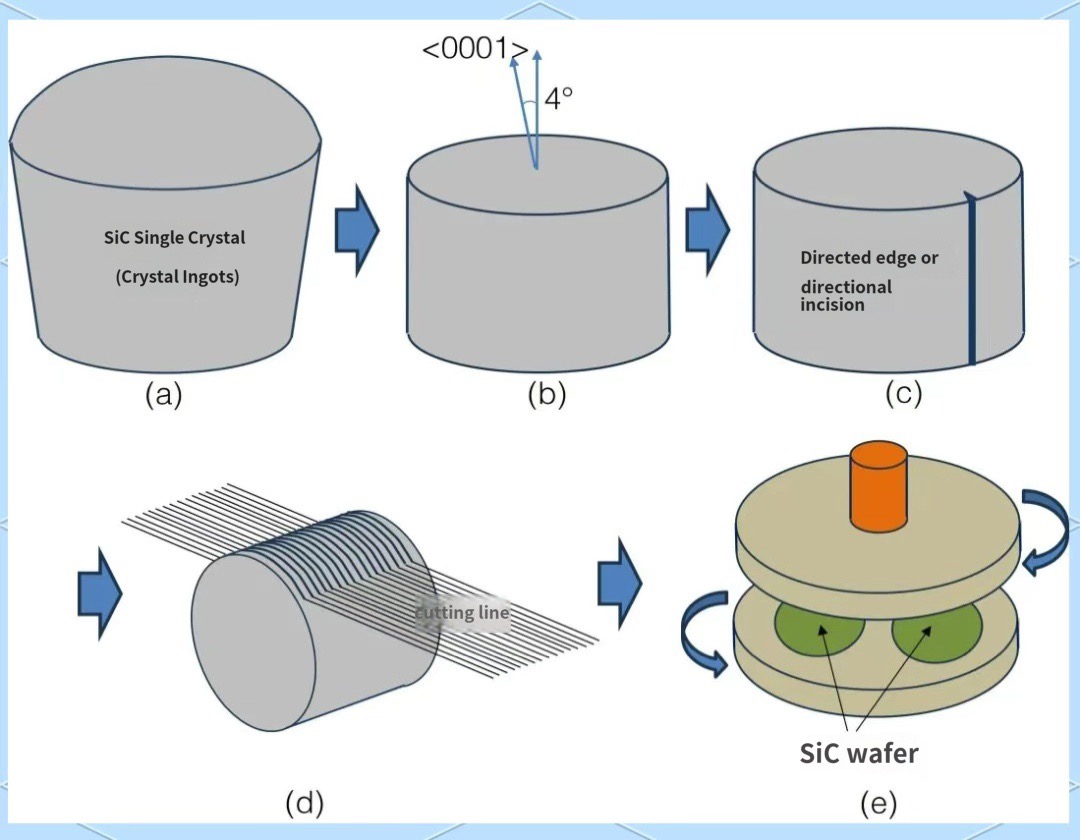

ການກຳນົດທິດທາງຂອງຜລຶກ ແລະ ການບົດເສັ້ນຜ່າສູນກາງພາຍນອກ: ກ່ອນການປຸງແຕ່ງ, ຕ້ອງກຳນົດທິດທາງຂອງຜລຶກຂອງແທ່ງ SiC. ຫຼັງຈາກນັ້ນ, ແທ່ງຈະຖືກປັ້ນເປັນໂຄງສ້າງຮູບຊົງກະບອກ (ທົ່ວໄປເອີ້ນວ່າ puck SiC) ຜ່ານການບົດເສັ້ນຜ່າສູນກາງພາຍນອກ. ຂັ້ນຕອນນີ້ຈະວາງພື້ນຖານສຳລັບການຕັດ ແລະ ການຊອຍຕາມທິດທາງຕໍ່ມາ.

ການຕັດຫຼາຍສາຍ: ວິທີການນີ້ໃຊ້ອະນຸພາກຂັດປະສົມກັບສາຍຕັດເພື່ອຕັດແທ່ງຮູບຊົງກະບອກ. ຢ່າງໃດກໍຕາມ, ມັນປະສົບກັບການສູນເສຍໂຄ້ງ ແລະ ບັນຫາຄວາມບໍ່ສະໝໍ່າສະເໝີຂອງພື້ນຜິວ.

ເຕັກໂນໂລຊີການຕັດດ້ວຍເລເຊີ: ເລເຊີຖືກນຳໃຊ້ເພື່ອສ້າງຊັ້ນທີ່ຖືກດັດແປງພາຍໃນຜລຶກ, ເຊິ່ງສາມາດແຍກຊິ້ນບາງໆອອກຈາກມັນໄດ້. ວິທີການນີ້ຊ່ວຍຫຼຸດຜ່ອນການສູນເສຍວັດສະດຸ ແລະ ເພີ່ມປະສິດທິພາບການປະມວນຜົນ, ເຮັດໃຫ້ມັນເປັນທິດທາງໃໝ່ທີ່ມີຄວາມຫວັງສຳລັບການຕັດແຜ່ນ SiC.

ການເພີ່ມປະສິດທິພາບຂອງຂະບວນການຕັດ

ການຕັດຫຼາຍສາຍໄຟທີ່ມີການຂັດຄົງທີ່: ປະຈຸບັນນີ້ແມ່ນເທັກໂນໂລຢີຫຼັກ, ເໝາະສົມກັບຄຸນລັກສະນະຄວາມແຂງສູງຂອງ SiC.

ເຕັກໂນໂລຊີການເຄື່ອງຈັກປ່ອຍໄຟຟ້າ (EDM) ແລະ ການແຍກເຢັນ: ວິທີການເຫຼົ່ານີ້ໃຫ້ວິທີແກ້ໄຂທີ່ຫຼາກຫຼາຍເຊິ່ງສອດຄ່ອງກັບຄວາມຕ້ອງການສະເພາະ.

ຂະບວນການຂັດເງົາ: ມັນເປັນສິ່ງຈຳເປັນທີ່ຈະຕ້ອງດຸ່ນດ່ຽງອັດຕາການກຳຈັດວັດສະດຸ ແລະ ຄວາມເສຍຫາຍຂອງພື້ນຜິວ. ການຂັດເງົາກົນຈັກທາງເຄມີ (CMP) ຖືກນໍາໃຊ້ເພື່ອປັບປຸງຄວາມສະໝໍ່າສະເໝີຂອງພື້ນຜິວ.

ການຕິດຕາມກວດກາແບບເວລາຈິງ: ເຕັກໂນໂລຊີການກວດກາທາງອອນໄລນ໌ໄດ້ຖືກນຳສະເໜີເພື່ອຕິດຕາມກວດກາຄວາມຫຍາບຂອງພື້ນຜິວແບບເວລາຈິງ.

ການຊອຍດ້ວຍເລເຊີ: ເຕັກນິກນີ້ຊ່ວຍຫຼຸດຜ່ອນການສູນເສຍ kerf ແລະຫຼຸດຮອບວຽນການປະມວນຜົນ, ເຖິງແມ່ນວ່າເຂດທີ່ໄດ້ຮັບຜົນກະທົບຈາກຄວາມຮ້ອນຍັງຄົງເປັນສິ່ງທ້າທາຍ.

ເຕັກໂນໂລຊີການປຸງແຕ່ງແບບປະສົມ: ການລວມວິທີການກົນຈັກ ແລະ ເຄມີເຂົ້າກັນຊ່ວຍເພີ່ມປະສິດທິພາບໃນການປຸງແຕ່ງ.

ເທັກໂນໂລຢີນີ້ໄດ້ບັນລຸການນຳໃຊ້ໃນອຸດສາຫະກຳແລ້ວ. ຕົວຢ່າງເຊັ່ນ Infineon ໄດ້ຊື້ SILTECTRA ແລະປະຈຸບັນຖືສິດທິບັດຫຼັກທີ່ສະໜັບສະໜູນການຜະລິດເວເຟີຂະໜາດ 8 ນິ້ວເປັນຈຳນວນຫຼາຍ. ໃນປະເທດຈີນ, ບໍລິສັດຕ່າງໆເຊັ່ນ Delong Laser ໄດ້ບັນລຸປະສິດທິພາບຜົນຜະລິດ 30 ເວເຟີຕໍ່ແທ່ງສຳລັບການປະມວນຜົນເວເຟີຂະໜາດ 6 ນິ້ວ, ເຊິ່ງເປັນຕົວແທນການປັບປຸງ 40% ເມື່ອທຽບກັບວິທີການແບບດັ້ງເດີມ.

ໃນຂະນະທີ່ການຜະລິດອຸປະກອນພາຍໃນປະເທດເລັ່ງຂຶ້ນ, ເຕັກໂນໂລຊີນີ້ຄາດວ່າຈະກາຍເປັນວິທີແກ້ໄຂຫຼັກສຳລັບການປຸງແຕ່ງຊັ້ນຮອງ SiC. ດ້ວຍເສັ້ນຜ່າສູນກາງຂອງວັດສະດຸເຄິ່ງຕົວນຳທີ່ເພີ່ມຂຶ້ນ, ວິທີການຕັດແບບດັ້ງເດີມກໍ່ກາຍເປັນລ້າສະໄໝ. ໃນບັນດາທາງເລືອກໃນປະຈຸບັນ, ເຕັກໂນໂລຊີເລື່ອຍສາຍເພັດແບບຕອບໂຕ້ສະແດງໃຫ້ເຫັນເຖິງໂອກາດການນຳໃຊ້ທີ່ມີຄວາມຫວັງທີ່ສຸດ. ການຕັດດ້ວຍເລເຊີ, ໃນຖານະເປັນເຕັກນິກທີ່ພົ້ນເດັ່ນຂຶ້ນມາ, ມີຂໍ້ໄດ້ປຽບທີ່ສຳຄັນ ແລະ ຄາດວ່າຈະກາຍເປັນວິທີການຕັດຫຼັກໃນອະນາຄົດ.

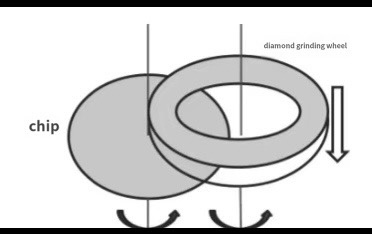

2,ການບົດ SiC ແບບຜລຶກດຽວ

ໃນຖານະທີ່ເປັນຕົວແທນຂອງເຄິ່ງຕົວນຳລຸ້ນທີສາມ, ຊິລິກອນຄາໄບ (SiC) ມີຂໍ້ໄດ້ປຽບທີ່ສຳຄັນເນື່ອງຈາກຊ່ອງຫວ່າງແບນວິດກວ້າງ, ສະໜາມໄຟຟ້າແຕກຫັກສູງ, ຄວາມໄວໃນການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນອີ່ມຕົວສູງ, ແລະ ຄວາມນຳຄວາມຮ້ອນທີ່ດີເລີດ. ຄຸນສົມບັດເຫຼົ່ານີ້ເຮັດໃຫ້ SiC ມີປະໂຫຍດໂດຍສະເພາະໃນການນຳໃຊ້ແຮງດັນສູງ (ເຊັ່ນ: ສະພາບແວດລ້ອມ 1200V). ເຕັກໂນໂລຊີການປະມວນຜົນສຳລັບຊັ້ນຮອງພື້ນ SiC ແມ່ນສ່ວນພື້ນຖານຂອງການຜະລິດອຸປະກອນ. ຄຸນນະພາບພື້ນຜິວ ແລະ ຄວາມແມ່ນຍຳຂອງຊັ້ນຮອງພື້ນມີຜົນກະທົບໂດຍກົງຕໍ່ຄຸນນະພາບຂອງຊັ້ນ epitaxial ແລະ ປະສິດທິພາບຂອງອຸປະກອນສຸດທ້າຍ.

ຈຸດປະສົງຫຼັກຂອງຂະບວນການບົດແມ່ນເພື່ອກຳຈັດຮອຍຂອງໜ້າດິນ ແລະ ຊັ້ນຄວາມເສຍຫາຍທີ່ເກີດຂຶ້ນໃນລະຫວ່າງການຕັດ, ແລະ ເພື່ອແກ້ໄຂການຜິດຮູບທີ່ເກີດຈາກຂະບວນການຕັດ. ເນື່ອງຈາກ SiC ມີຄວາມແຂງສູງຫຼາຍ, ການບົດຮຽກຮ້ອງໃຫ້ມີການໃຊ້ສານຂັດແຂງເຊັ່ນ: ໂບຣອນຄາໄບ ຫຼື ເພັດ. ການບົດແບບທຳມະດາມັກຈະແບ່ງອອກເປັນການບົດຫຍາບ ແລະ ການບົດລະອຽດ.

2.1 ການບົດຫຍາບ ແລະ ການບົດລະອຽດ

ການບົດສາມາດຈັດປະເພດໄດ້ໂດຍອີງໃສ່ຂະໜາດຂອງອະນຸພາກຂັດ:

ການບົດຫຍາບ: ໃຊ້ສານຂັດຂະໜາດໃຫຍ່ກວ່າເພື່ອກຳຈັດຮອຍເລື່ອຍ ແລະ ຊັ້ນຄວາມເສຍຫາຍທີ່ເກີດຂຶ້ນໃນລະຫວ່າງການຕັດ, ປັບປຸງປະສິດທິພາບໃນການປະມວນຜົນ.

ການບົດລະອຽດ: ໃຊ້ສານຂັດທີ່ລະອຽດກວ່າເພື່ອກຳຈັດຊັ້ນຄວາມເສຍຫາຍທີ່ເຫຼືອຈາກການບົດຫຍາບ, ຫຼຸດຜ່ອນຄວາມຫຍາບຂອງພື້ນຜິວ, ແລະ ປັບປຸງຄຸນນະພາບຂອງພື້ນຜິວ.

ຜູ້ຜະລິດຊັ້ນຮອງພື້ນ SiC ພາຍໃນປະເທດຫຼາຍແຫ່ງໃຊ້ຂະບວນການຜະລິດຂະໜາດໃຫຍ່. ວິທີການທົ່ວໄປກ່ຽວຂ້ອງກັບການບົດສອງດ້ານໂດຍໃຊ້ແຜ່ນເຫຼັກຫລໍ່ ແລະ ນ້ຳຢາເພັດ monocrystalline. ຂະບວນການນີ້ຈະກຳຈັດຊັ້ນຄວາມເສຍຫາຍທີ່ເຫຼືອຈາກການເລື່ອຍລວດ, ແກ້ໄຂຮູບຮ່າງຂອງແຜ່ນ wafer, ແລະ ຫຼຸດຜ່ອນ TTV (ການປ່ຽນແປງຄວາມໜາທັງໝົດ), Bow, ແລະ Warp. ອັດຕາການກຳຈັດວັດສະດຸແມ່ນໝັ້ນຄົງ, ໂດຍປົກກະຕິແລ້ວຈະບັນລຸ 0.8–1.2 μm/ນາທີ. ຢ່າງໃດກໍຕາມ, ໜ້າຜິວແຜ່ນ wafer ທີ່ໄດ້ຮັບແມ່ນດ້ານທີ່ມີຄວາມຫຍາບຂ້ອນຂ້າງສູງ - ໂດຍປົກກະຕິແລ້ວປະມານ 50 nm - ເຊິ່ງເຮັດໃຫ້ມີຄວາມຕ້ອງການສູງຂຶ້ນໃນຂັ້ນຕອນການຂັດເງົາຕໍ່ມາ.

2.2 ການຂັດດ້ານດຽວ

ການບົດແບບດ້ານດຽວຈະປະມວນຜົນພຽງແຕ່ດ້ານດຽວຂອງແຜ່ນເວເຟີໃນແຕ່ລະຄັ້ງ. ໃນລະຫວ່າງຂະບວນການນີ້, ແຜ່ນເວເຟີຈະຖືກຕິດດ້ວຍຂີ້ເຜີ້ງໃສ່ແຜ່ນເຫຼັກ. ພາຍໃຕ້ຄວາມກົດດັນທີ່ນຳໃຊ້, ພື້ນຜິວຈະເກີດການຜິດຮູບເລັກນ້ອຍ, ແລະ ໜ້າຜິວດ້ານເທິງຈະຮາບພຽງ. ຫຼັງຈາກການບົດ, ໜ້າຜິວດ້ານລຸ່ມຈະຮາບພຽງ. ເມື່ອຄວາມກົດດັນຖືກກຳຈັດອອກ, ໜ້າຜິວດ້ານເທິງມັກຈະກັບຄືນສູ່ຮູບຮ່າງເດີມ, ເຊິ່ງຍັງສົ່ງຜົນກະທົບຕໍ່ໜ້າຜິວດ້ານລຸ່ມທີ່ບົດແລ້ວ - ເຮັດໃຫ້ທັງສອງດ້ານບິດເບືອນ ແລະ ເສື່ອມສະພາບໃນຄວາມຮາບພຽງ.

ຍິ່ງໄປກວ່ານັ້ນ, ແຜ່ນບົດສາມາດກາຍເປັນຮູບໂຄ້ງໄດ້ໃນເວລາສັ້ນໆ, ເຮັດໃຫ້ແຜ່ນເວເຟີກາຍເປັນຮູບນູນ. ເພື່ອຮັກສາຄວາມຮາບພຽງຂອງແຜ່ນ, ຈຳເປັນຕ້ອງມີການບົດເລື້ອຍໆ. ເນື່ອງຈາກປະສິດທິພາບຕໍ່າ ແລະ ຄວາມຮາບພຽງຂອງແຜ່ນເວເຟີທີ່ບໍ່ດີ, ການບົດດ້ານດຽວຈຶ່ງບໍ່ເໝາະສົມສຳລັບການຜະລິດເປັນຈຳນວນຫຼາຍ.

ໂດຍປົກກະຕິແລ້ວ, ລໍ້ຂັດ #8000 ຖືກນໍາໃຊ້ສໍາລັບການຂັດລະອຽດ. ໃນປະເທດຍີ່ປຸ່ນ, ຂະບວນການນີ້ແມ່ນຂ້ອນຂ້າງແກ່ຍາວແລະແມ່ນແຕ່ໃຊ້ລໍ້ຂັດ #30000. ສິ່ງນີ້ຊ່ວຍໃຫ້ຄວາມຫຍາບຂອງພື້ນຜິວຂອງແຜ່ນເວເຟີທີ່ຜ່ານການປຸງແຕ່ງສາມາດບັນລຸໄດ້ຕໍ່າກວ່າ 2 nm, ເຮັດໃຫ້ແຜ່ນເວເຟີພ້ອມທີ່ຈະສໍາລັບ CMP ສຸດທ້າຍ (ການຂັດດ້ວຍກົນຈັກເຄມີ) ໂດຍບໍ່ຕ້ອງຜ່ານການປຸງແຕ່ງເພີ່ມເຕີມ.

2.3 ເຕັກໂນໂລຊີການເຮັດໃຫ້ບາງລົງດ້ານດຽວ

ເທັກໂນໂລຢີການເຮັດໃຫ້ບາງລົງດ້ວຍເພັດດ້ານດຽວແມ່ນວິທີການໃໝ່ຂອງການບົດດ້ານດຽວ. ດັ່ງທີ່ສະແດງຢູ່ໃນຮູບທີ 5 (ບໍ່ໄດ້ສະແດງຢູ່ນີ້), ຂະບວນການນີ້ໃຊ້ແຜ່ນບົດທີ່ຜູກມັດດ້ວຍເພັດ. ແຜ່ນເວເຟີຖືກຕິດຕັ້ງຜ່ານການດູດຊຶມສູນຍາກາດ, ໃນຂະນະທີ່ທັງແຜ່ນເວເຟີ ແລະ ລໍ້ບົດເພັດໝຸນພ້ອມໆກັນ. ລໍ້ບົດຈະຄ່ອຍໆເຄື່ອນລົງເພື່ອເຮັດໃຫ້ແຜ່ນເວເຟີບາງລົງຕາມຄວາມໜາເປົ້າໝາຍ. ຫຼັງຈາກດ້ານໜຶ່ງສຳເລັດແລ້ວ, ແຜ່ນເວເຟີຈະຖືກພິກເພື່ອປະມວນຜົນອີກດ້ານໜຶ່ງ.

ຫຼັງຈາກການເຮັດໃຫ້ບາງລົງ, ເວເຟີ 100 ມມ ສາມາດບັນລຸ:

ໂຄ້ງ < 5 μm

TTV < 2 ໄມໂຄຣມ

ຄວາມຫຍາບຂອງພື້ນຜິວ < 1 nm

ວິທີການປະມວນຜົນແຜ່ນເວເຟີດ່ຽວນີ້ມີຄວາມໝັ້ນຄົງສູງ, ຄວາມສອດຄ່ອງທີ່ດີເລີດ, ແລະອັດຕາການກຳຈັດວັດສະດຸສູງ. ເມື່ອປຽບທຽບກັບການບົດສອງດ້ານແບບດັ້ງເດີມ, ເຕັກນິກນີ້ຊ່ວຍປັບປຸງປະສິດທິພາບການບົດໄດ້ຫຼາຍກວ່າ 50%.

2.4 ການຂັດສອງດ້ານ

ການຂັດສອງດ້ານໃຊ້ທັງແຜ່ນຂັດດ້ານເທິງ ແລະ ດ້ານລຸ່ມເພື່ອຂັດທັງສອງດ້ານຂອງວັດສະດຸພ້ອມໆກັນ, ຮັບປະກັນຄຸນນະພາບພື້ນຜິວທີ່ດີເລີດທັງສອງດ້ານ.

ໃນລະຫວ່າງຂະບວນການ, ແຜ່ນບົດຈະໃຊ້ແຮງກົດດັນໃສ່ຈຸດສູງສຸດຂອງຊິ້ນວຽກກ່ອນ, ເຊິ່ງເຮັດໃຫ້ເກີດການຜິດຮູບ ແລະ ຄ່ອຍໆກຳຈັດວັດສະດຸອອກຢູ່ຈຸດເຫຼົ່ານັ້ນ. ເມື່ອຈຸດສູງຖືກປັບລະດັບ, ແຮງກົດດັນໃສ່ຊັ້ນວາງຈະຄ່ອຍໆເປັນເອກະພາບຫຼາຍຂຶ້ນ, ເຊິ່ງເຮັດໃຫ້ເກີດການຜິດຮູບທີ່ສອດຄ່ອງກັນທົ່ວພື້ນຜິວທັງໝົດ. ສິ່ງນີ້ຊ່ວຍໃຫ້ທັງພື້ນຜິວດ້ານເທິງ ແລະ ດ້ານລຸ່ມສາມາດບົດໄດ້ຢ່າງເທົ່າທຽມກັນ. ເມື່ອການບົດສຳເລັດ ແລະ ແຮງກົດດັນຖືກປ່ອຍອອກ, ແຕ່ລະສ່ວນຂອງຊັ້ນວາງຈະຟື້ນຕົວຢ່າງເປັນເອກະພາບຍ້ອນແຮງກົດດັນທີ່ເທົ່າກັນ. ສິ່ງນີ້ນຳໄປສູ່ການບິດເບືອນໜ້ອຍທີ່ສຸດ ແລະ ຄວາມຮາບພຽງດີ.

ຄວາມຫຍາບຂອງພື້ນຜິວຂອງແຜ່ນເວເຟີຫຼັງຈາກການບົດແມ່ນຂຶ້ນກັບຂະໜາດຂອງອະນຸພາກທີ່ມີສີຂັດ - ອະນຸພາກຂະໜາດນ້ອຍກວ່າຈະເຮັດໃຫ້ພື້ນຜິວລຽບກວ່າ. ເມື່ອໃຊ້ສານຂັດ 5 μm ສຳລັບການບົດສອງດ້ານ, ຄວາມຮາບພຽງຂອງແຜ່ນເວເຟີ ແລະ ການປ່ຽນແປງຄວາມໜາສາມາດຄວບຄຸມໄດ້ພາຍໃນ 5 μm. ການວັດແທກດ້ວຍກ້ອງຈຸລະທັດແຮງປະລໍາມະນູ (AFM) ສະແດງໃຫ້ເຫັນຄວາມຫຍາບຂອງພື້ນຜິວ (Rq) ປະມານ 100 nm, ມີຂຸມບົດເລິກເຖິງ 380 nm ແລະ ມີຮອຍເສັ້ນຊື່ທີ່ເຫັນໄດ້ທີ່ເກີດຈາກການກະທຳທີ່ມີສີຂັດ.

ວິທີການທີ່ກ້າວໜ້າກວ່ານັ້ນກ່ຽວຂ້ອງກັບການບົດສອງດ້ານໂດຍໃຊ້ແຜ່ນໂຟມໂພລີຢູຣີເທນປະສົມກັບນ້ຳຢາເພັດໂພລີຄຣິສຕາລິນ. ຂະບວນການນີ້ຜະລິດແຜ່ນເວເຟີທີ່ມີຄວາມຫຍາບຂອງພື້ນຜິວຕໍ່າຫຼາຍ, ບັນລຸ Ra < 3 nm, ເຊິ່ງເປັນປະໂຫຍດຫຼາຍສຳລັບການຂັດເງົາຂອງຊັ້ນຮອງພື້ນ SiC ຕໍ່ມາ.

ເຖິງຢ່າງໃດກໍ່ຕາມ, ຮອຍຂີດຂ່ວນເທິງໜ້າດິນຍັງຄົງເປັນບັນຫາທີ່ຍັງບໍ່ໄດ້ຮັບການແກ້ໄຂ. ນອກຈາກນັ້ນ, ເພັດ polycrystalline ທີ່ໃຊ້ໃນຂະບວນການນີ້ແມ່ນຜະລິດຜ່ານການສັງເຄາະລະເບີດ, ເຊິ່ງມີຄວາມທ້າທາຍທາງດ້ານເຕັກນິກ, ໃຫ້ຜົນຜະລິດໃນປະລິມານຕໍ່າ, ແລະ ມີລາຄາແພງຫຼາຍ.

ການຂັດເງົາຂອງຜລຶກ SiC ດ່ຽວ

ເພື່ອໃຫ້ໄດ້ຮັບພື້ນຜິວທີ່ຂັດເງົາທີ່ມີຄຸນນະພາບສູງເທິງແຜ່ນຊິລິກອນຄາໄບ (SiC), ການຂັດເງົາຕ້ອງກຳຈັດຂຸມບົດ ແລະ ການເຄື່ອນທີ່ຂອງພື້ນຜິວຂະໜາດນາໂນແມັດອອກໃຫ້ໝົດ. ເປົ້າໝາຍແມ່ນເພື່ອສ້າງພື້ນຜິວທີ່ລຽບນຽນ, ບໍ່ມີຂໍ້ບົກຜ່ອງໂດຍບໍ່ມີການປົນເປື້ອນ ຫຼື ການເຊື່ອມໂຊມ, ບໍ່ມີຄວາມເສຍຫາຍຕໍ່ພື້ນຜິວໃຕ້ດິນ, ແລະ ບໍ່ມີຄວາມກົດດັນທີ່ຕົກຄ້າງຢູ່ພື້ນຜິວ.

3.1 ການຂັດເງົາກົນຈັກ ແລະ CMP ຂອງແຜ່ນ SiC

ຫຼັງຈາກການເຕີບໂຕຂອງແທ່ງຜລຶກດ່ຽວ SiC, ຂໍ້ບົກຜ່ອງດ້ານໜ້າປ້ອງກັນບໍ່ໃຫ້ມັນຖືກນໍາໃຊ້ໂດຍກົງສໍາລັບການເຕີບໂຕຂອງ epitaxial. ດັ່ງນັ້ນ, ຈຶ່ງຕ້ອງມີການປະມວນຜົນຕື່ມອີກ. ແທ່ງຈະຖືກປັ້ນເປັນຮູບຊົງກະບອກມາດຕະຖານໂດຍຜ່ານການມົນ, ຈາກນັ້ນຕັດເປັນແຜ່ນແພໂດຍໃຊ້ການຕັດລວດ, ຕາມດ້ວຍການຢັ້ງຢືນທິດທາງຂອງຜລຶກ. ການຂັດເງົາເປັນຂັ້ນຕອນທີ່ສໍາຄັນໃນການປັບປຸງຄຸນນະພາບແຜ່ນແພ, ແກ້ໄຂຄວາມເສຍຫາຍດ້ານໜ້າດິນທີ່ອາດເກີດຂຶ້ນຈາກຂໍ້ບົກຜ່ອງດ້ານການເຕີບໂຕຂອງຜລຶກ ແລະ ຂັ້ນຕອນການປະມວນຜົນກ່ອນໜ້ານີ້.

ມີສີ່ວິທີຫຼັກໃນການກຳຈັດຊັ້ນຄວາມເສຍຫາຍຂອງໜ້າດິນເທິງ SiC:

ການຂັດເງົາດ້ວຍກົນຈັກ: ງ່າຍດາຍແຕ່ປະໄວ້ຮອຍຂີດຂ່ວນ; ເໝາະສຳລັບການຂັດເງົາໃນເບື້ອງຕົ້ນ.

ການຂັດເງົາກົນຈັກທາງເຄມີ (CMP): ກຳຈັດຮອຍຂີດຂ່ວນໂດຍການກັດດ້ວຍສານເຄມີ; ເໝາະສຳລັບການຂັດເງົາແບບແມ່ນຍຳສູງ.

ການແກະສະຫຼັກໄຮໂດຣເຈນ: ຕ້ອງການອຸປະກອນທີ່ສັບສົນ, ເຊິ່ງມັກໃຊ້ໃນຂະບວນການ HTCVD.

ການຂັດເງົາດ້ວຍພລາສມາ: ສະລັບສັບຊ້ອນ ແລະ ບໍ່ຄ່ອຍໄດ້ໃຊ້.

ການຂັດດ້ວຍກົນຈັກເທົ່ານັ້ນມັກຈະເຮັດໃຫ້ເກີດຮອຍຂີດຂ່ວນ, ໃນຂະນະທີ່ການຂັດດ້ວຍສານເຄມີເທົ່ານັ້ນສາມາດນໍາໄປສູ່ການແກະສະຫຼັກທີ່ບໍ່ສະໝໍ່າສະເໝີ. CMP ລວມເອົາທັງສອງຂໍ້ດີ ແລະ ສະເໜີວິທີແກ້ໄຂທີ່ມີປະສິດທິພາບ ແລະ ປະຫຍັດຕົ້ນທຶນ.

ຫຼັກການເຮັດວຽກຂອງ CMP

CMP ເຮັດວຽກໂດຍການໝຸນແຜ່ນເວເຟີພາຍໃຕ້ຄວາມກົດດັນທີ່ກຳນົດໄວ້ຕໍ່ກັບແຜ່ນຂັດທີ່ໝຸນ. ການເຄື່ອນໄຫວທີ່ກ່ຽວຂ້ອງນີ້, ບວກກັບການຂັດທາງກົນຈັກຈາກສານຂັດຂະໜາດນາໂນໃນນ້ຳຢາ ແລະ ການເຄື່ອນໄຫວທາງເຄມີຂອງຕົວແທນທີ່ມີປະຕິກິລິຍາ, ບັນລຸຄວາມລຽບຂອງພື້ນຜິວ.

ວັດສະດຸຫຼັກທີ່ໃຊ້:

ນ້ຳຢາຂັດ: ປະກອບດ້ວຍສານຂັດ ແລະ ສານປະຕິກິລິຍາທາງເຄມີ.

ຜ້າຂັດ: ຈະເສື່ອມສະພາບໃນລະຫວ່າງການໃຊ້ງານ, ຊ່ວຍຫຼຸດຂະໜາດຂອງຮູຂຸມຂົນ ແລະ ປະສິດທິພາບໃນການລະບາຍນ້ຳຢາ. ຕ້ອງໃຊ້ເຄື່ອງຂັດເປັນປະຈຳ, ໂດຍປົກກະຕິແລ້ວແມ່ນໃຊ້ເຄື່ອງຂັດເພັດ, ເພື່ອຟື້ນຟູຄວາມຫຍາບ.

ຂະບວນການ CMP ທົ່ວໄປ

ການຂັດ: ນ້ຳຢາເພັດ 0.5 μm

ຄວາມຫຍາບຂອງພື້ນຜິວເປົ້າໝາຍ: ~0.7 nm

ການຂັດເງົາທາງເຄມີ:

ອຸປະກອນຂັດ: ເຄື່ອງຂັດດ້ານດຽວ AP-810

ຄວາມດັນ: 200 ກຣາມ/ຊມ²

ຄວາມໄວຂອງແຜ່ນ: 50 rpm

ຄວາມໄວຂອງຕົວຍຶດເຊລາມິກ: 38 rpm

ສ່ວນປະກອບຂອງນ້ຳລະລາຍ:

SiO₂ (30 wt%, pH = 10.15)

0–70 wt% H₂O₂ (30 wt%, ເກຣດສານເຮັດປະຕິກິລິຍາ)

ປັບ pH ໃຫ້ຢູ່ທີ່ 8.5 ໂດຍໃຊ້ KOH 5 wt% ແລະ HNO₃ 1 wt%

ອັດຕາການໄຫຼຂອງນໍ້າເປື້ອນ: 3 ລິດ/ນາທີ, ໄຫຼວຽນຄືນ

ຂະບວນການນີ້ປັບປຸງຄຸນນະພາບຂອງແຜ່ນ SiC ຢ່າງມີປະສິດທິພາບ ແລະ ຕອບສະໜອງຄວາມຕ້ອງການສຳລັບຂະບວນການຕໍ່ເນື່ອງ.

ສິ່ງທ້າທາຍດ້ານເຕັກນິກໃນການຂັດເງົາກົນຈັກ

SiC, ໃນຖານະເປັນເຄິ່ງຕົວນຳທີ່ມີແຖບຄວາມຖີ່ກ້ວາງ, ມີບົດບາດສຳຄັນໃນອຸດສາຫະກຳເອເລັກໂຕຣນິກ. ດ້ວຍຄຸນສົມບັດທາງກາຍະພາບ ແລະ ເຄມີທີ່ດີເລີດ, ຜລຶກຊິລິກາດ່ຽວ SiC ຈຶ່ງເໝາະສົມສຳລັບສະພາບແວດລ້ອມທີ່ຮຸນແຮງ, ເຊັ່ນ: ອຸນຫະພູມສູງ, ຄວາມຖີ່ສູງ, ພະລັງງານສູງ, ແລະ ຄວາມຕ້ານທານລັງສີ. ຢ່າງໃດກໍຕາມ, ລັກສະນະແຂງ ແລະ ແຕກຫັກງ່າຍຂອງມັນເຮັດໃຫ້ເກີດສິ່ງທ້າທາຍອັນໃຫຍ່ຫຼວງສຳລັບການບົດ ແລະ ຂັດເງົາ.

ໃນຂະນະທີ່ຜູ້ຜະລິດຊັ້ນນໍາຂອງໂລກໄດ້ຫັນປ່ຽນຈາກແຜ່ນເວເຟີຂະໜາດ 6 ນິ້ວມາເປັນ 8 ນິ້ວ, ບັນຫາຕ່າງໆເຊັ່ນ: ການແຕກ ແລະ ຄວາມເສຍຫາຍຂອງແຜ່ນເວເຟີໃນລະຫວ່າງການປຸງແຕ່ງໄດ້ກາຍເປັນທີ່ໂດດເດັ່ນຫຼາຍຂຶ້ນ, ເຊິ່ງສົ່ງຜົນກະທົບຢ່າງຫຼວງຫຼາຍຕໍ່ຜົນຜະລິດ. ການແກ້ໄຂບັນຫາທາງດ້ານເຕັກນິກຂອງຊັ້ນວາງ SiC ຂະໜາດ 8 ນິ້ວໃນປັດຈຸບັນແມ່ນມາດຕະຖານທີ່ສໍາຄັນສໍາລັບຄວາມກ້າວໜ້າຂອງອຸດສາຫະກໍາ.

ໃນຍຸກ 8 ນິ້ວ, ການປະມວນຜົນແຜ່ນ SiC ປະເຊີນກັບສິ່ງທ້າທາຍຫຼາຍຢ່າງ:

ການຂະຫຍາຍແຜ່ນເວເຟີແມ່ນມີຄວາມຈຳເປັນເພື່ອເພີ່ມຜົນຜະລິດຂອງຊິບຕໍ່ຊຸດ, ຫຼຸດຜ່ອນການສູນເສຍຂອບ, ແລະ ຫຼຸດຜ່ອນຕົ້ນທຶນການຜະລິດ - ໂດຍສະເພາະແມ່ນຍ້ອນຄວາມຕ້ອງການທີ່ເພີ່ມຂຶ້ນໃນການນຳໃຊ້ລົດໄຟຟ້າ.

ໃນຂະນະທີ່ການເຕີບໂຕຂອງຜລຶກ SiC ດ່ຽວຂະໜາດ 8 ນິ້ວໄດ້ເຕີບໃຫຍ່ເຕັມທີ່ແລ້ວ, ຂະບວນການດ້ານຫຼັງເຊັ່ນ: ການບົດ ແລະ ການຂັດຍັງປະເຊີນກັບບັນຫາຄໍຂວດ, ເຊິ່ງສົ່ງຜົນໃຫ້ຜົນຜະລິດຕໍ່າ (ພຽງແຕ່ 40–50%).

ເວເຟີຂະໜາດໃຫຍ່ກວ່າຈະມີການແຈກຢາຍຄວາມກົດດັນທີ່ສັບສົນຫຼາຍຂຶ້ນ, ເຊິ່ງເພີ່ມຄວາມຫຍຸ້ງຍາກໃນການຈັດການຄວາມກົດດັນໃນການຂັດເງົາ ແລະ ຄວາມສອດຄ່ອງຂອງຜົນຜະລິດ.

ເຖິງແມ່ນວ່າຄວາມໜາຂອງແຜ່ນເວເຟີຂະໜາດ 8 ນິ້ວຈະໃກ້ຄຽງກັບຄວາມໜາຂອງແຜ່ນເວເຟີຂະໜາດ 6 ນິ້ວ, ແຕ່ພວກມັນມັກຈະເກີດຄວາມເສຍຫາຍໃນລະຫວ່າງການຈັບຕ້ອງຍ້ອນຄວາມກົດດັນ ແລະ ການບິດເບືອນ.

ເພື່ອຫຼຸດຜ່ອນຄວາມກົດດັນ, ການບິດງໍ, ແລະ ການແຕກທີ່ກ່ຽວຂ້ອງກັບການຕັດ, ການຕັດດ້ວຍເລເຊີຈຶ່ງຖືກນຳໃຊ້ເພີ່ມຂຶ້ນເລື້ອຍໆ. ຢ່າງໃດກໍຕາມ:

ເລເຊີຄວາມຍາວຄື່ນຍາວເຮັດໃຫ້ເກີດຄວາມເສຍຫາຍຈາກຄວາມຮ້ອນ.

ເລເຊີຄື້ນສັ້ນສ້າງຊາກຫັກພັງໜັກ ແລະ ເລິກລົງສູ່ຊັ້ນຄວາມເສຍຫາຍ, ເພີ່ມຄວາມສັບສົນໃນການຂັດເງົາ.

ຂະບວນການຂັດເງົາກົນຈັກສຳລັບ SiC

ຂະບວນການທົ່ວໄປປະກອບມີ:

ການຕັດທິດທາງ

ການບົດຫຍາບ

ການບົດລະອຽດ

ການຂັດເງົາດ້ວຍກົນຈັກ

ການຂັດເງົາກົນຈັກທາງເຄມີ (CMP) ເປັນຂັ້ນຕອນສຸດທ້າຍ

ການເລືອກວິທີການ CMP, ການອອກແບບເສັ້ນທາງຂະບວນການ, ແລະ ການເພີ່ມປະສິດທິພາບຂອງພາລາມິເຕີແມ່ນມີຄວາມສຳຄັນຫຼາຍ. ໃນການຜະລິດເຄິ່ງຕົວນຳ, CMP ແມ່ນຂັ້ນຕອນທີ່ກຳນົດສຳລັບການຜະລິດແຜ່ນ SiC ທີ່ມີພື້ນຜິວທີ່ລຽບນຽນ, ບໍ່ມີຂໍ້ບົກຜ່ອງ, ແລະ ບໍ່ມີຄວາມເສຍຫາຍ, ເຊິ່ງມີຄວາມຈຳເປັນສຳລັບການເຕີບໂຕຂອງ epitaxial ທີ່ມີຄຸນນະພາບສູງ.

(ກ) ເອົາແທ່ງ SiC ອອກຈາກໝໍ້ຫຸງ;

(ຂ) ປະຕິບັດການປັ້ນຮູບຮ່າງເບື້ອງຕົ້ນໂດຍໃຊ້ການບົດເສັ້ນຜ່າສູນກາງພາຍນອກ;

(ຄ) ກຳນົດທິດທາງຂອງຜລຶກໂດຍໃຊ້ຮູບແບບຮາບພຽງ ຫຼື ຮອຍບ່ຽງ;

(ງ) ຊອຍແທ່ງເປັນແຜ່ນບາງໆໂດຍໃຊ້ເລື່ອຍຫຼາຍເສັ້ນລວດ;

(ອ) ບັນລຸຄວາມລຽບນຽນຂອງພື້ນຜິວຄືກັບກະຈົກຜ່ານຂັ້ນຕອນການບົດ ແລະ ການຂັດ.

ຫຼັງຈາກສຳເລັດຂັ້ນຕອນການປຸງແຕ່ງຊຸດໜຶ່ງແລ້ວ, ຂອບດ້ານນອກຂອງແຜ່ນ SiC ມັກຈະຄົມ, ເຊິ່ງເພີ່ມຄວາມສ່ຽງຕໍ່ການບิ่นໃນລະຫວ່າງການຈັບ ຫຼື ການນຳໃຊ້. ເພື່ອຫຼີກເວັ້ນຄວາມບອບບາງດັ່ງກ່າວ, ຈຳເປັນຕ້ອງມີການບົດຂອບ.

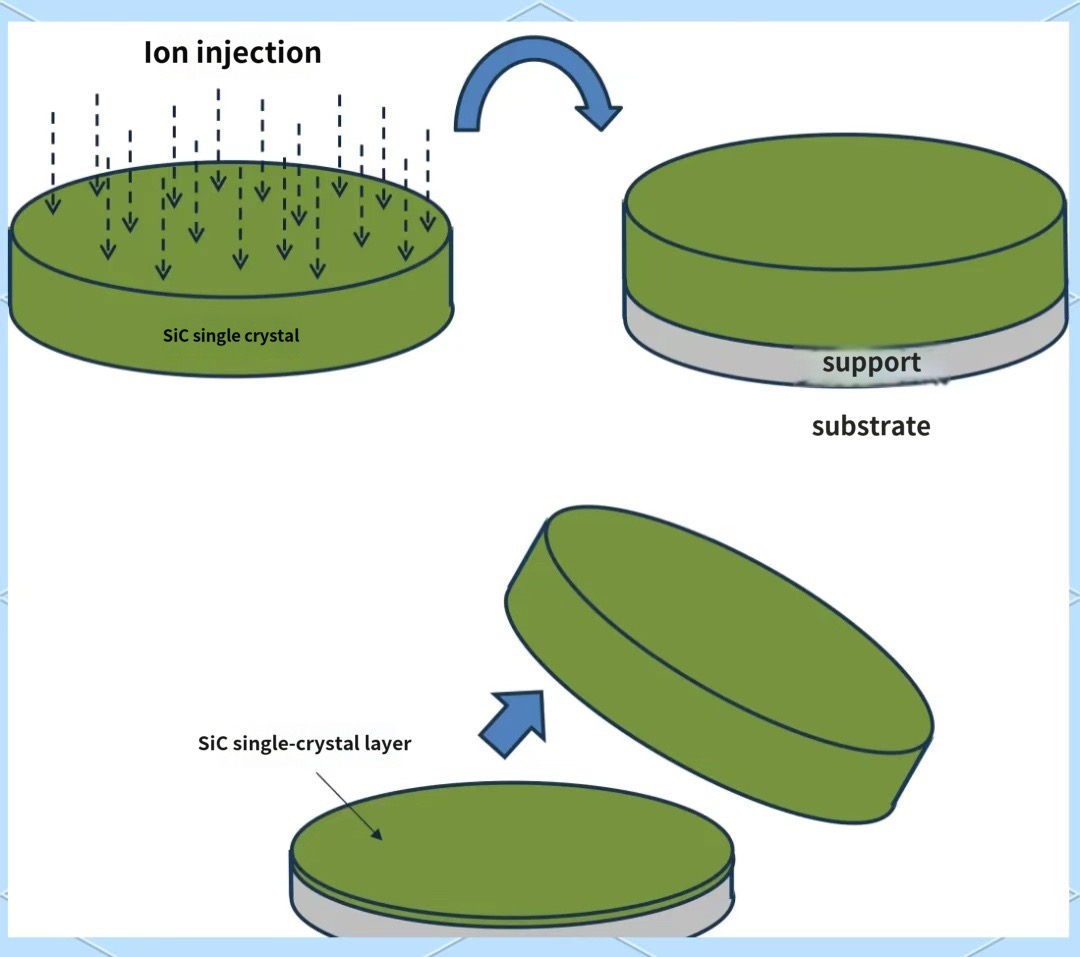

ນອກເໜືອໄປຈາກຂະບວນການຕັດແບບດັ້ງເດີມ, ວິທີການໃໝ່ສຳລັບການກະກຽມແຜ່ນ SiC ຍັງກ່ຽວຂ້ອງກັບເຕັກໂນໂລຊີການຜູກມັດ. ວິທີການນີ້ຊ່ວຍໃຫ້ການຜະລິດແຜ່ນໄດ້ໂດຍການຜູກມັດຊັ້ນຜລຶກດຽວ SiC ບາງໆກັບຊັ້ນຮອງພື້ນທີ່ບໍ່ເປັນເອກະພາບ (ຊັ້ນຮອງພື້ນ).

ຮູບທີ 3 ສະແດງໃຫ້ເຫັນເຖິງຂະບວນການ:

ທຳອິດ, ຊັ້ນການແຍກສ່ວນຈະຖືກສ້າງຕັ້ງຂຶ້ນໃນຄວາມເລິກທີ່ກຳນົດໄວ້ເທິງໜ້າດິນຂອງຜລຶກດ່ຽວ SiC ໂດຍຜ່ານການຝັງໄອອອນໄຮໂດຣເຈນ ຫຼື ເຕັກນິກທີ່ຄ້າຍຄືກັນ. ຫຼັງຈາກນັ້ນຜລຶກດ່ຽວ SiC ທີ່ຖືກປຸງແຕ່ງແລ້ວຈະຖືກຜູກມັດກັບຊັ້ນຮອງຮັບທີ່ຮາບພຽງ ແລະ ຢູ່ພາຍໃຕ້ຄວາມກົດດັນ ແລະ ຄວາມຮ້ອນ. ສິ່ງນີ້ຊ່ວຍໃຫ້ສາມາດໂອນ ແລະ ແຍກຊັ້ນຜລຶກດ່ຽວ SiC ໄປໃສ່ຊັ້ນຮອງຮັບໄດ້ຢ່າງສຳເລັດຜົນ.

ຊັ້ນ SiC ທີ່ແຍກອອກມານັ້ນຈະຜ່ານການປຸງແຕ່ງໜ້າດິນເພື່ອໃຫ້ໄດ້ຄວາມຮາບພຽງຕາມທີ່ຕ້ອງການ ແລະ ສາມາດນຳມາໃຊ້ຄືນໃນຂະບວນການຜູກມັດຕໍ່ໄປ. ເມື່ອປຽບທຽບກັບການຕັດຜລຶກ SiC ແບບດັ້ງເດີມ, ເຕັກນິກນີ້ຊ່ວຍຫຼຸດຜ່ອນຄວາມຕ້ອງການວັດສະດຸທີ່ມີລາຄາແພງ. ເຖິງແມ່ນວ່າຍັງມີສິ່ງທ້າທາຍດ້ານເຕັກນິກຢູ່, ແຕ່ການຄົ້ນຄວ້າ ແລະ ພັດທະນາກຳລັງກ້າວໜ້າຢ່າງຕັ້ງໜ້າເພື່ອເຮັດໃຫ້ສາມາດຜະລິດແຜ່ນເວເຟີທີ່ມີລາຄາຖືກກວ່າ.

ເນື່ອງຈາກຄວາມແຂງສູງ ແລະ ຄວາມໝັ້ນຄົງທາງເຄມີຂອງ SiC—ເຊິ່ງເຮັດໃຫ້ມັນທົນທານຕໍ່ປະຕິກິລິຍາຢູ່ທີ່ອຸນຫະພູມຫ້ອງ—ຈຶ່ງຈຳເປັນຕ້ອງມີການຂັດເງົາກົນຈັກເພື່ອກຳຈັດຂຸມບົດລະອຽດ, ຫຼຸດຜ່ອນຄວາມເສຍຫາຍຂອງພື້ນຜິວ, ກຳຈັດຮອຍຂີດຂ່ວນ, ຂຸມ, ແລະ ຂໍ້ບົກຜ່ອງຂອງເປືອກສົ້ມ, ຫຼຸດຜ່ອນຄວາມຫຍາບຂອງພື້ນຜິວ, ປັບປຸງຄວາມລຽບ, ແລະ ເສີມຂະຫຍາຍຄຸນນະພາບຂອງພື້ນຜິວ.

ເພື່ອໃຫ້ໄດ້ພື້ນຜິວທີ່ຂັດເງົາທີ່ມີຄຸນນະພາບສູງ, ມັນຈຳເປັນຕ້ອງ:

ປັບປະເພດຂັດ,

ຫຼຸດຂະໜາດຂອງອະນຸພາກ,

ເພີ່ມປະສິດທິພາບພາລາມິເຕີຂອງຂະບວນການ,

ເລືອກວັດສະດຸຂັດ ແລະ ແຜ່ນຂັດທີ່ມີຄວາມແຂງພຽງພໍ.

ຮູບທີ 7 ສະແດງໃຫ້ເຫັນວ່າການຂັດສອງດ້ານດ້ວຍສານຂັດ 1 μm ສາມາດຄວບຄຸມຄວາມຮາບພຽງ ແລະ ການປ່ຽນແປງຄວາມໜາພາຍໃນ 10 μm, ແລະ ຫຼຸດຜ່ອນຄວາມຫຍາບຂອງພື້ນຜິວໃຫ້ເຫຼືອປະມານ 0.25 nm.

3.2 ການຂັດເງົາກົນຈັກທາງເຄມີ (CMP)

ການຂັດເງົາກົນຈັກທາງເຄມີ (CMP) ປະສົມປະສານການຂັດຂູດຂອງອະນຸພາກທີ່ມີຄວາມລະອຽດອ່ອນຫຼາຍກັບການແກະສະຫຼັກທາງເຄມີເພື່ອສ້າງພື້ນຜິວທີ່ລຽບ ແລະ ຮາບພຽງຢູ່ເທິງວັດສະດຸທີ່ກຳລັງປຸງແຕ່ງ. ຫຼັກການພື້ນຖານແມ່ນ:

ປະຕິກິລິຍາເຄມີເກີດຂຶ້ນລະຫວ່າງນ້ຳຢາຂັດເງົາ ແລະ ໜ້າດິນແຜ່ນເວເຟີ, ປະກອບເປັນຊັ້ນອ່ອນ.

ແຮງສຽດທານລະຫວ່າງອະນຸພາກທີ່ມີສານຂັດ ແລະ ຊັ້ນອ່ອນໆຈະເຮັດໃຫ້ວັດສະດຸຖືກກຳຈັດອອກ.

ຂໍ້ໄດ້ປຽບຂອງ CMP:

ເອົາຊະນະຂໍ້ເສຍຂອງການຂັດເງົາດ້ວຍກົນຈັກ ຫຼື ສານເຄມີຢ່າງດຽວ,

ບັນລຸທັງການວາງແຜນທົ່ວໂລກ ແລະ ທ້ອງຖິ່ນ,

ຜະລິດພື້ນຜິວທີ່ມີຄວາມຮາບພຽງສູງ ແລະ ຄວາມຫຍາບຕໍ່າ,

ບໍ່ເຮັດໃຫ້ເກີດຄວາມເສຍຫາຍຕໍ່ພື້ນຜິວ ຫຼື ພື້ນຜິວໃຕ້ດິນ.

ລາຍລະອຽດ:

ແຜ່ນເວເຟີເຄື່ອນທີ່ທຽບກັບແຜ່ນຂັດພາຍໃຕ້ຄວາມກົດດັນ.

ສານເຄມີຂັດຂະໜາດນາໂນແມັດ (ເຊັ່ນ SiO₂) ໃນນໍ້າຢາມີສ່ວນຊ່ວຍໃນການຕັດ, ເຮັດໃຫ້ພັນທະໂຄວາເລນ Si-C ອ່ອນແອລົງ ແລະ ເສີມຂະຫຍາຍການກຳຈັດວັດສະດຸ.

ປະເພດຂອງເຕັກນິກ CMP:

ການຂັດເງົາແບບອິດສະຫຼະ: ວັດສະດຸຂັດ (ເຊັ່ນ SiO₂) ຖືກລະລາຍໃນນໍ້າລາຍ. ການກຳຈັດວັດສະດຸເກີດຂຶ້ນຜ່ານການຂັດເງົາສາມຕົວ (ແຜ່ນແຜ່ນ-ແຜ່ນຂັດ). ຂະໜາດຂອງວັດສະດຸຂັດ (ໂດຍປົກກະຕິ 60–200 nm), pH, ແລະອຸນຫະພູມຕ້ອງໄດ້ຮັບການຄວບຄຸມຢ່າງຊັດເຈນເພື່ອປັບປຸງຄວາມສະໝໍ່າສະເໝີ.

ການຂັດເງົາແບບຄົງທີ່: ນ້ຳຢາຂັດຖືກຝັງຢູ່ໃນແຜ່ນຂັດເພື່ອປ້ອງກັນການລວມຕົວກັນ - ເໝາະສຳລັບການປະມວນຜົນທີ່ມີຄວາມແມ່ນຍໍາສູງ.

ການເຮັດຄວາມສະອາດຫຼັງການຂັດເງົາ:

ເວເຟີທີ່ຂັດເງົາຜ່ານ:

ການເຮັດຄວາມສະອາດທາງເຄມີ (ລວມທັງການກຳຈັດນ້ຳ DI ແລະ ສິ່ງເສດເຫຼືອຂອງແຫຼວ),

ການລ້າງດ້ວຍນ້ຳ DI, ແລະ

ການອົບແຫ້ງດ້ວຍໄນໂຕຣເຈນຮ້ອນ

ເພື່ອຫຼຸດຜ່ອນສິ່ງປົນເປື້ອນເທິງໜ້າດິນ.

ຄຸນນະພາບ ແລະ ປະສິດທິພາບຂອງພື້ນຜິວ

ຄວາມຫຍາບຂອງພື້ນຜິວສາມາດຫຼຸດລົງເປັນ Ra < 0.3 nm, ຕອບສະໜອງຄວາມຕ້ອງການຂອງການ epitaxy ຂອງເຄິ່ງຕົວນຳ.

ການເຮັດໃຫ້ເປັນຮູບຊົງກົມທົ່ວໂລກ: ການປະສົມປະສານຂອງການເຮັດໃຫ້ອ່ອນລົງດ້ວຍສານເຄມີ ແລະ ການກຳຈັດດ້ວຍກົນຈັກຊ່ວຍຫຼຸດຜ່ອນຮອຍຂີດຂ່ວນ ແລະ ການແກະສະຫຼັກທີ່ບໍ່ສະເໝີກັນ, ເຊິ່ງມີປະສິດທິພາບດີກວ່າວິທີການກົນຈັກ ຫຼື ເຄມີທີ່ບໍລິສຸດ.

ປະສິດທິພາບສູງ: ເໝາະສຳລັບວັດສະດຸແຂງ ແລະ ແຕກຫັກງ່າຍ ເຊັ່ນ: SiC, ດ້ວຍອັດຕາການກຳຈັດວັດສະດຸສູງກວ່າ 200 nm/h.

ເຕັກນິກການຂັດເງົາທີ່ພົ້ນເດັ່ນຂຶ້ນອື່ນໆ

ນອກເໜືອໄປຈາກ CMP ແລ້ວ, ຍັງມີການສະເໜີວິທີການທາງເລືອກອື່ນໆ, ລວມທັງ:

ການຂັດເງົາດ້ວຍໄຟຟ້າເຄມີ, ການຂັດເງົາດ້ວຍຕົວເລັ່ງປະຕິກິລິຍາ ຫຼື ການແກະສະຫຼັກ, ແລະ

ການຂັດເງົາແບບໄຕຣໂບເຄມີ.

ເຖິງຢ່າງໃດກໍ່ຕາມ, ວິທີການເຫຼົ່ານີ້ຍັງຢູ່ໃນຂັ້ນຕອນການຄົ້ນຄວ້າ ແລະ ໄດ້ພັດທະນາຊ້າໆຍ້ອນຄຸນສົມບັດຂອງວັດສະດຸທີ່ທ້າທາຍຂອງ SiC.

ໃນທີ່ສຸດ, ການປຸງແຕ່ງ SiC ແມ່ນຂະບວນການທີ່ຄ່ອຍໆເປັນໄປໃນການຫຼຸດຜ່ອນຄວາມບິດເບືອນ ແລະ ຄວາມຫຍາບຄາຍເພື່ອປັບປຸງຄຸນນະພາບຂອງພື້ນຜິວ, ບ່ອນທີ່ການຄວບຄຸມຄວາມຮາບພຽງ ແລະ ຄວາມຫຍາບຄາຍແມ່ນມີຄວາມສໍາຄັນຫຼາຍຕະຫຼອດແຕ່ລະຂັ້ນຕອນ.

ເຕັກໂນໂລຊີການປຸງແຕ່ງ

ໃນລະຫວ່າງຂັ້ນຕອນການບົດແຜ່ນເວເຟີ, ນ້ຳຢາເພັດທີ່ມີຂະໜາດອະນຸພາກແຕກຕ່າງກັນຈະຖືກນຳໃຊ້ເພື່ອບົດແຜ່ນເວເຟີໃຫ້ໄດ້ຄວາມຮາບພຽງ ແລະ ຄວາມຫຍາບຂອງພື້ນຜິວຕາມທີ່ຕ້ອງການ. ຫຼັງຈາກນັ້ນ, ໂດຍການຂັດເງົາ, ໂດຍໃຊ້ທັງເຕັກນິກການຂັດເງົາກົນຈັກ ແລະ ເຄມີ (CMP) ເພື່ອຜະລິດແຜ່ນເວເຟີຊິລິກອນຄາໄບ (SiC) ທີ່ຂັດເງົາບໍ່ເສຍຫາຍ.

ຫຼັງຈາກການຂັດເງົາ, ແຜ່ນຊິລິໂຄນຈະຖືກກວດກາຄຸນນະພາບຢ່າງເຂັ້ມງວດໂດຍໃຊ້ເຄື່ອງມືເຊັ່ນ: ກ້ອງຈຸລະທັດແບບ optical ແລະ ເຄື່ອງວັດແທກການກະຈາຍລັງສີເອັກສ໌ ເພື່ອຮັບປະກັນວ່າຕົວກໍານົດການທາງເທັກນິກທັງໝົດຕອບສະໜອງມາດຕະຖານທີ່ກໍານົດໄວ້. ສຸດທ້າຍ, ແຜ່ນຊິລິໂຄນທີ່ຂັດເງົາແລ້ວຈະຖືກທໍາຄວາມສະອາດໂດຍໃຊ້ນໍ້າຢາທໍາຄວາມສະອາດພິເສດ ແລະ ນໍ້າບໍລິສຸດພິເສດເພື່ອກໍາຈັດສິ່ງປົນເປື້ອນເທິງໜ້າດິນ. ຫຼັງຈາກນັ້ນ, ພວກມັນຖືກເຮັດໃຫ້ແຫ້ງໂດຍໃຊ້ອາຍແກັສໄນໂຕຣເຈນທີ່ມີຄວາມບໍລິສຸດສູງພິເສດ ແລະ ເຄື່ອງອົບແຫ້ງແບບໝຸນ, ເຊິ່ງເຮັດໃຫ້ຂະບວນການຜະລິດທັງໝົດສໍາເລັດ.

ຫຼັງຈາກຄວາມພະຍາຍາມຫຼາຍປີ, ມີຄວາມຄືບໜ້າຢ່າງຫຼວງຫຼາຍໃນການປຸງແຕ່ງຜລຶກດ່ຽວ SiC ພາຍໃນປະເທດຈີນ. ພາຍໃນປະເທດ, ຜລຶກດ່ຽວ 4H-SiC ທີ່ມີສານກັນຄວາມຮ້ອນເຄິ່ງ 100 ມມ ໄດ້ຖືກພັດທະນາຢ່າງສຳເລັດຜົນ, ແລະ ຜລຶກດ່ຽວປະເພດ n 4H-SiC ແລະ 6H-SiC ສາມາດຜະລິດເປັນຊຸດໄດ້ແລ້ວ. ບໍລິສັດຕ່າງໆເຊັ່ນ TankeBlue ແລະ TYST ໄດ້ພັດທະນາຜລຶກດ່ຽວ SiC ຂະໜາດ 150 ມມ ແລ້ວ.

ໃນດ້ານເຕັກໂນໂລຊີການປຸງແຕ່ງແຜ່ນເວເຟີ SiC, ສະຖາບັນພາຍໃນປະເທດໄດ້ຄົ້ນຄວ້າເງື່ອນໄຂຂະບວນການ ແລະ ເສັ້ນທາງສຳລັບການຊອຍ, ການບົດ ແລະ ການຂັດເງົາ. ພວກເຂົາສາມາດຜະລິດຕົວຢ່າງທີ່ຕອບສະໜອງຄວາມຕ້ອງການສຳລັບການຜະລິດອຸປະກອນໄດ້. ຢ່າງໃດກໍຕາມ, ເມື່ອທຽບກັບມາດຕະຖານສາກົນ, ຄຸນນະພາບການປຸງແຕ່ງພື້ນຜິວຂອງແຜ່ນເວເຟີພາຍໃນປະເທດຍັງຢູ່ຫຼັງຫຼາຍ. ມີບັນຫາຫຼາຍຢ່າງຄື:

ທິດສະດີ SiC ແລະ ເຕັກໂນໂລຊີການປຸງແຕ່ງສາກົນແມ່ນໄດ້ຮັບການປົກປ້ອງຢ່າງເຂັ້ມງວດ ແລະ ບໍ່ສາມາດເຂົ້າເຖິງໄດ້ງ່າຍ.

ຍັງຂາດການຄົ້ນຄວ້າທາງທິດສະດີ ແລະ ການສະໜັບສະໜູນສຳລັບການປັບປຸງ ແລະ ການເພີ່ມປະສິດທິພາບຂອງຂະບວນການ.

ຄ່າໃຊ້ຈ່າຍໃນການນໍາເຂົ້າອຸປະກອນແລະສ່ວນປະກອບຈາກຕ່າງປະເທດແມ່ນສູງ.

ການຄົ້ນຄວ້າພາຍໃນປະເທດກ່ຽວກັບການອອກແບບອຸປະກອນ, ຄວາມແມ່ນຍໍາໃນການປຸງແຕ່ງ, ແລະ ວັດສະດຸຍັງສະແດງໃຫ້ເຫັນຊ່ອງຫວ່າງທີ່ສຳຄັນເມື່ອທຽບກັບລະດັບສາກົນ.

ປະຈຸບັນ, ເຄື່ອງມືທີ່ມີຄວາມແມ່ນຍໍາສູງສ່ວນໃຫຍ່ທີ່ໃຊ້ໃນປະເທດຈີນແມ່ນນໍາເຂົ້າ. ອຸປະກອນ ແລະ ວິທີການທົດສອບຍັງຕ້ອງການການປັບປຸງຕື່ມອີກ.

ດ້ວຍການພັດທະນາຢ່າງຕໍ່ເນື່ອງຂອງເຄິ່ງຕົວນຳລຸ້ນທີສາມ, ເສັ້ນຜ່າສູນກາງຂອງຊັ້ນຮອງຜລຶກດ່ຽວ SiC ກຳລັງເພີ່ມຂຶ້ນຢ່າງຕໍ່ເນື່ອງ, ພ້ອມກັບຄວາມຕ້ອງການທີ່ສູງຂຶ້ນສຳລັບຄຸນນະພາບການປະມວນຜົນພື້ນຜິວ. ເຕັກໂນໂລຊີການປະມວນຜົນແຜ່ນເວເຟີໄດ້ກາຍເປັນໜຶ່ງໃນຂັ້ນຕອນທີ່ທ້າທາຍທາງດ້ານເຕັກນິກທີ່ສຸດຫຼັງຈາກການເຕີບໂຕຂອງຜລຶກດ່ຽວ SiC.

ເພື່ອແກ້ໄຂບັນຫາທ້າທາຍທີ່ມີຢູ່ໃນການປຸງແຕ່ງ, ມັນເປັນສິ່ງຈໍາເປັນທີ່ຈະຕ້ອງສຶກສາເພີ່ມເຕີມກ່ຽວກັບກົນໄກທີ່ກ່ຽວຂ້ອງກັບການຕັດ, ການບົດ, ແລະການຂັດ, ແລະເພື່ອຄົ້ນຫາວິທີການແລະເສັ້ນທາງຂະບວນການທີ່ເໝາະສົມສໍາລັບການຜະລິດແຜ່ນ SiC. ໃນເວລາດຽວກັນ, ມັນເປັນສິ່ງຈໍາເປັນທີ່ຈະຕ້ອງຮຽນຮູ້ຈາກເຕັກໂນໂລຊີການປຸງແຕ່ງສາກົນທີ່ກ້າວຫນ້າແລະນໍາໃຊ້ເຕັກນິກເຄື່ອງຈັກແລະອຸປະກອນທີ່ມີຄວາມແມ່ນຍໍາສູງທີ່ທັນສະໄໝເພື່ອຜະລິດວັດສະດຸທີ່ມີຄຸນນະພາບສູງ.

ເມື່ອຂະໜາດຂອງແຜ່ນເວເຟີເພີ່ມຂຶ້ນ, ຄວາມຫຍຸ້ງຍາກໃນການເຕີບໂຕຂອງຜລຶກ ແລະ ການປຸງແຕ່ງກໍ່ເພີ່ມຂຶ້ນເຊັ່ນກັນ. ເຖິງຢ່າງໃດກໍ່ຕາມ, ປະສິດທິພາບການຜະລິດຂອງອຸປະກອນຕ່າງໆຈະດີຂຶ້ນຢ່າງຫຼວງຫຼາຍ, ແລະ ຕົ້ນທຶນຕໍ່ໜ່ວຍກໍ່ຫຼຸດລົງ. ໃນປະຈຸບັນ, ຜູ້ສະໜອງແຜ່ນເວເຟີ SiC ຫຼັກໆໃນທົ່ວໂລກສະເໜີຜະລິດຕະພັນທີ່ມີເສັ້ນຜ່າສູນກາງຕັ້ງແຕ່ 4 ນິ້ວ ຫາ 6 ນິ້ວ. ບໍລິສັດຊັ້ນນຳເຊັ່ນ Cree ແລະ II-VI ໄດ້ເລີ່ມຕົ້ນວາງແຜນການພັດທະນາສາຍການຜະລິດແຜ່ນເວເຟີ SiC ຂະໜາດ 8 ນິ້ວແລ້ວ.

ເວລາໂພສ: ພຶດສະພາ-23-2025