4 ນິ້ວ SiC Wafers 6H Semi-Insulating SiC Substrates prime, ການຄົ້ນຄວ້າ, ແລະຊັ້ນຮຽນ dummy

ຂໍ້ມູນຈໍາເພາະຂອງຜະລິດຕະພັນ

| ເກຣດ | ເກຣດການຜະລິດ MPD (Z Grade) | ລະດັບການຜະລິດມາດຕະຖານ (P Grade) | ເກຣດ Dummy (D Grade) | ||||||||

| ເສັ້ນຜ່າສູນກາງ | 99.5 mm ~ 100.0 mm | ||||||||||

| 4H-SI | 500 μm± 20 μm | 500 μm± 25 μm | |||||||||

| Wafer ປະຖົມນິເທດ |

Off axis : 4.0° ໄປຫາ< 1120 > ±0.5° ສໍາລັບ 4H-N, On axis : <0001>±0.5° ສໍາລັບ 4H-SI | ||||||||||

| 4H-SI | ≤1ຊມ-2 | ≤5ຊມ-2 | ≤15ຊມ-2 | ||||||||

| 4H-SI | ≥1E9 Ω·ຊມ | ≥1E5 Ω·ຊມ | |||||||||

| ປະຖົມນິເທດ Flat ປະຖົມ | {10-10} ±5.0° | ||||||||||

| ຄວາມຍາວຮາບພຽງຕົ້ນຕໍ | 32.5 ມມ ± 2.0 ມມ | ||||||||||

| ຄວາມຍາວຮາບພຽງຮອງ | 18.0 ມມ ± 2.0 ມມ | ||||||||||

| ປະຖົມນິເທດແບນມັດທະຍົມ | Silicon ປະເຊີນຫນ້າ: 90 ° CW. ຈາກ Prime flat ±5.0° | ||||||||||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | ||||||||||

| LTV/TTV/Bow/Warp | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| ຄວາມຫຍາບຄາຍ | C ໜ້າ | ໂປໂລຍ | Ra≤1 nm | ||||||||

| Si face | CMP | Ra≤0.2 nm | Ra≤0.5nm | ||||||||

| ຂອບຮອຍແຕກໂດຍແສງສະຫວ່າງທີ່ມີຄວາມເຂັ້ມຂຸ້ນສູງ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤ 10 ມມ, ດ່ຽວ ຄວາມຍາວ≤2ມມ | |||||||||

| ແຜ່ນ Hex ໂດຍແສງສະຫວ່າງທີ່ມີຄວາມເຂັ້ມຂຸ້ນສູງ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.1% | |||||||||

| ພື້ນທີ່ Polytype ໂດຍແສງສະຫວ່າງທີ່ມີຄວາມເຂັ້ມຂຸ້ນສູງ | ບໍ່ມີ | ພື້ນທີ່ສະສົມ≤3% | |||||||||

| ການລວມ Carbon Visual | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤3% | |||||||||

| ຮອຍຂີດຂ່ວນຂອງພື້ນຜິວ Silicon ໂດຍແສງສະຫວ່າງທີ່ມີຄວາມເຂັ້ມຂຸ້ນສູງ | ບໍ່ມີ | ຄວາມຍາວສະສົມ≤1*ເສັ້ນຜ່າສູນກາງ wafer | |||||||||

| Edge Chips ສູງໂດຍຄວາມເຂັ້ມຂອງແສງ | ບໍ່ອະນຸຍາດໃຫ້ມີ ≥0.2 mm width ແລະຄວາມເລິກ | 5 ອະນຸຍາດ, ≤1ມມແຕ່ລະຄົນ | |||||||||

| ການປົນເປື້ອນພື້ນຜິວ Silicon ໂດຍຄວາມເຂັ້ມຂົ້ນສູງ | ບໍ່ມີ | ||||||||||

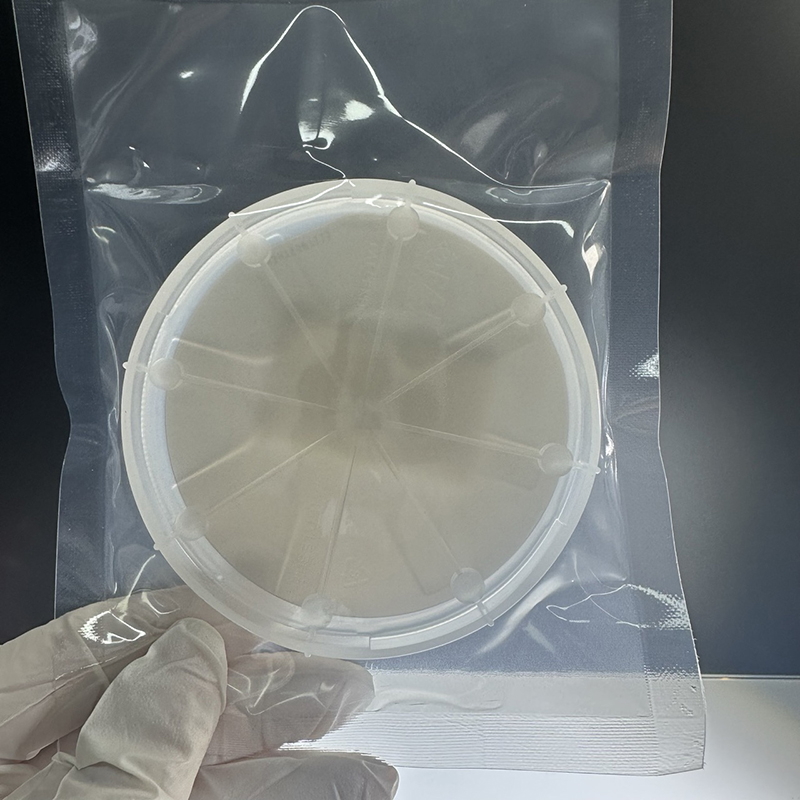

| ການຫຸ້ມຫໍ່ | Multi-wafer Cassette ຫຼື Wafer ດຽວ Container | ||||||||||

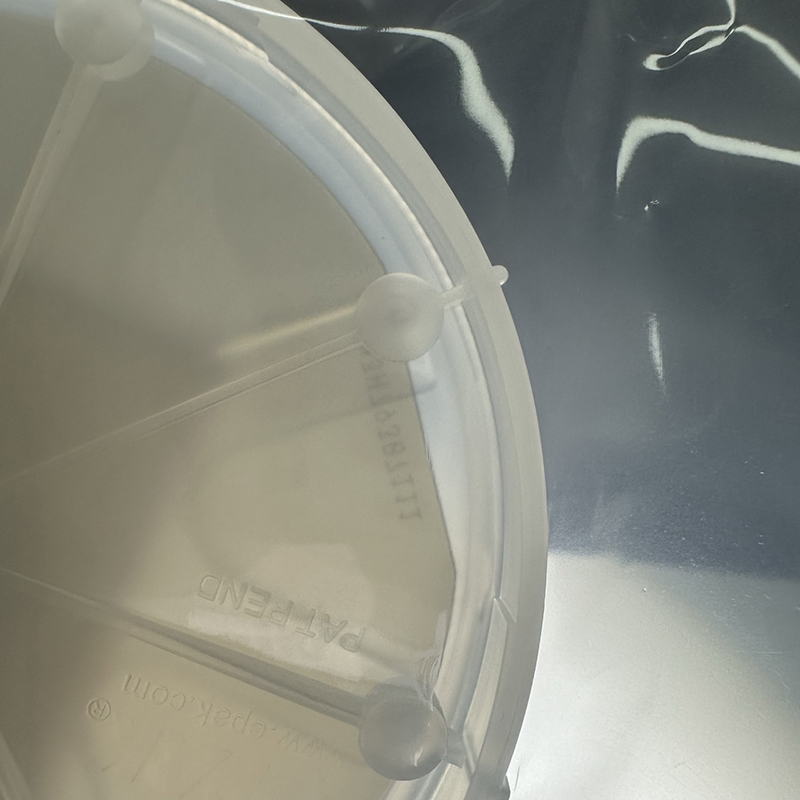

ແຜນວາດລາຍລະອຽດ

ຜະລິດຕະພັນທີ່ກ່ຽວຂ້ອງ

ຂຽນຂໍ້ຄວາມຂອງທ່ານທີ່ນີ້ແລະສົ່ງໃຫ້ພວກເຮົາ