ໃນຂະບວນການພັດທະນາທີ່ກຳລັງຂະຫຍາຍຕົວຂອງອຸດສາຫະກຳເຄິ່ງຕົວນຳ, ຜລຶກດຽວທີ່ຂັດເງົາເວເຟີຊິລິກອນມີບົດບາດສຳຄັນ. ພວກມັນເຮັດໜ້າທີ່ເປັນວັດສະດຸພື້ນຖານສຳລັບການຜະລິດອຸປະກອນໄມໂຄຣເອເລັກໂຕຣນິກຕ່າງໆ. ຕັ້ງແຕ່ວົງຈອນປະສົມປະສານທີ່ສັບສົນ ແລະ ຊັດເຈນ ຈົນເຖິງໄມໂຄຣໂປເຊດເຊີຄວາມໄວສູງ ແລະ ເຊັນເຊີຫຼາຍໜ້າທີ່, ຜລຶກດຽວທີ່ຂັດເງົາເວເຟີຊິລິກອນແມ່ນມີຄວາມຈຳເປັນ. ຄວາມແຕກຕ່າງໃນປະສິດທິພາບ ແລະ ລາຍລະອຽດຂອງພວກມັນສົ່ງຜົນກະທົບໂດຍກົງຕໍ່ຄຸນນະພາບ ແລະ ປະສິດທິພາບຂອງຜະລິດຕະພັນສຸດທ້າຍ. ຂ້າງລຸ່ມນີ້ແມ່ນລາຍລະອຽດ ແລະ ພາລາມິເຕີທົ່ວໄປຂອງແຜ່ນຊິລິໂຄນຜລຶກດຽວທີ່ຂັດເງົາ:

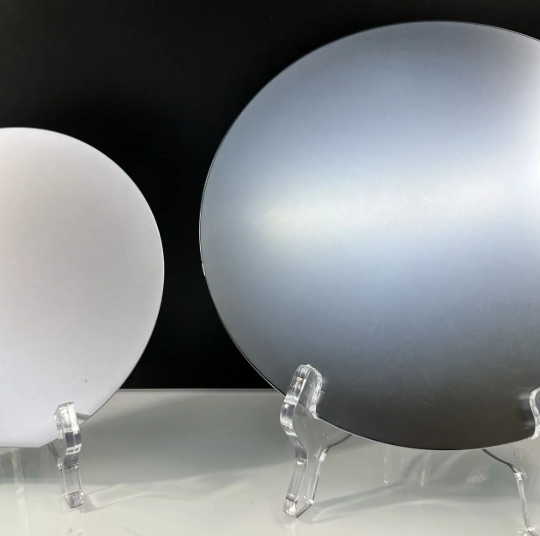

ເສັ້ນຜ່າສູນກາງ: ຂະໜາດຂອງເວເຟີຊິລິໂຄນແບບຜະນຶກດຽວແບບເຄິ່ງຕົວນຳຖືກວັດແທກໂດຍເສັ້ນຜ່າສູນກາງຂອງມັນ, ແລະພວກມັນມີຫຼາຍລາຍລະອຽດ. ເສັ້ນຜ່າສູນກາງທົ່ວໄປປະກອບມີ 2 ນິ້ວ (50.8 ມມ), 3 ນິ້ວ (76.2 ມມ), 4 ນິ້ວ (100 ມມ), 5 ນິ້ວ (125 ມມ), 6 ນິ້ວ (150 ມມ), 8 ນິ້ວ (200 ມມ), 12 ນິ້ວ (300 ມມ), ແລະ 18 ນິ້ວ (450 ມມ). ເສັ້ນຜ່າສູນກາງທີ່ແຕກຕ່າງກັນແມ່ນເໝາະສົມກັບຄວາມຕ້ອງການການຜະລິດ ແລະ ຄວາມຕ້ອງການຂອງຂະບວນການຕ່າງໆ. ຕົວຢ່າງ, ເວເຟີເສັ້ນຜ່າສູນກາງຂະໜາດນ້ອຍກວ່າມັກຖືກນຳໃຊ້ທົ່ວໄປສຳລັບອຸປະກອນໄມໂຄຣເອເລັກໂຕຣນິກພິເສດທີ່ມີປະລິມານໜ້ອຍ, ໃນຂະນະທີ່ເວເຟີເສັ້ນຜ່າສູນກາງຂະໜາດໃຫຍ່ສະແດງໃຫ້ເຫັນປະສິດທິພາບການຜະລິດທີ່ສູງຂຶ້ນ ແລະ ຂໍ້ໄດ້ປຽບດ້ານຕົ້ນທຶນໃນການຜະລິດວົງຈອນລວມຂະໜາດໃຫຍ່. ຄວາມຕ້ອງການຂອງພື້ນຜິວຖືກຈັດປະເພດເປັນຂັດດ້ານດຽວ (SSP) ແລະ ຂັດສອງດ້ານ (DSP). ເວເຟີຂັດດ້ານດຽວຖືກນຳໃຊ້ສຳລັບອຸປະກອນທີ່ຕ້ອງການຄວາມຮາບພຽງສູງຢູ່ດ້ານໜຶ່ງ, ເຊັ່ນ: ເຊັນເຊີບາງຊະນິດ. ເວເຟີຂັດສອງດ້ານມັກຖືກນຳໃຊ້ທົ່ວໄປສຳລັບວົງຈອນລວມ ແລະ ຜະລິດຕະພັນອື່ນໆທີ່ຕ້ອງການຄວາມແມ່ນຍຳສູງໃນທັງສອງພື້ນຜິວ. ຄວາມຕ້ອງການຂອງພື້ນຜິວ (ສຳເລັດຮູບ): SSP ຂັດດ້ານດຽວ / DSP ຂັດສອງດ້ານ.

ປະເພດ/ສານເສີມ: (1) ເຄິ່ງຕົວນຳປະເພດ N: ເມື່ອອະຕອມສິ່ງເຈືອປົນບາງຊະນິດຖືກນຳເຂົ້າໄປໃນເຄິ່ງຕົວນຳພາຍໃນ, ພວກມັນຈະປ່ຽນແປງຄວາມນຳໄຟຟ້າຂອງມັນ. ຕົວຢ່າງ, ເມື່ອມີອົງປະກອບ pentavalent ເຊັ່ນ: ໄນໂຕຣເຈນ (N), ຟອສຟໍຣັດ (P), ທາດອາເຊນິກ (As), ຫຼື ແອນຕິໂມນີ (Sb) ຖືກເພີ່ມເຂົ້າ, ເອເລັກຕຣອນວາເລນຂອງພວກມັນຈະສ້າງພັນທະໂຄວາເລນກັບເອເລັກຕຣອນວາເລນຂອງອະຕອມຊິລິກອນອ້ອມຂ້າງ, ເຮັດໃຫ້ເອເລັກຕຣອນເພີ່ມເຕີມບໍ່ຖືກຜູກມັດໂດຍພັນທະໂຄວາເລນ. ສິ່ງນີ້ເຮັດໃຫ້ຄວາມເຂັ້ມຂຸ້ນຂອງເອເລັກຕຣອນສູງກວ່າຄວາມເຂັ້ມຂຸ້ນຂອງຮູ, ປະກອບເປັນເຄິ່ງຕົວນຳປະເພດ N, ເຊິ່ງເອີ້ນກັນວ່າເຄິ່ງຕົວນຳປະເພດເອເລັກຕຣອນ. ເຄິ່ງຕົວນຳປະເພດ N ມີຄວາມສຳຄັນໃນການຜະລິດອຸປະກອນທີ່ຕ້ອງການເອເລັກຕຣອນເປັນຕົວນຳປະຈຸຫຼັກ, ເຊັ່ນ: ອຸປະກອນພະລັງງານບາງຢ່າງ. (2) ເຄິ່ງຕົວນຳປະເພດ P: ເມື່ອອົງປະກອບສິ່ງເຈືອປົນໄຕວາເລນເຊັ່ນ: ໂບຣອນ (B), ແກລຽມ (Ga), ຫຼື ອິນດຽມ (In) ຖືກນຳເຂົ້າໄປໃນເຄິ່ງຕົວນຳຊິລິກອນ, ເອເລັກຕຣອນວາເລນຂອງອະຕອມສິ່ງເຈືອປົນຈະສ້າງພັນທະໂຄວາເລນກັບອະຕອມຊິລິກອນອ້ອມຂ້າງ, ແຕ່ພວກມັນຂາດເອເລັກຕຣອນວາເລນຢ່າງໜ້ອຍໜຶ່ງຕົວ ແລະ ບໍ່ສາມາດສ້າງພັນທະໂຄວາເລນທີ່ສົມບູນໄດ້. ສິ່ງນີ້ນຳໄປສູ່ຄວາມເຂັ້ມຂຸ້ນຂອງຮູທີ່ສູງກວ່າຄວາມເຂັ້ມຂຸ້ນຂອງເອເລັກຕຣອນ, ປະກອບເປັນເຄິ່ງຕົວນຳປະເພດ P, ເຊິ່ງເອີ້ນກັນວ່າເຄິ່ງຕົວນຳປະເພດຮູ. ເຄິ່ງຕົວນຳປະເພດ P ມີບົດບາດສຳຄັນໃນການຜະລິດອຸປະກອນທີ່ຮູເຮັດໜ້າທີ່ເປັນຕົວນຳປະຈຸຫຼັກ, ເຊັ່ນ: ໄດໂອດ ແລະ ທຣານຊິດເຕີບາງຊະນິດ.

ຄວາມຕ້ານທານ: ຄວາມຕ້ານທານແມ່ນປະລິມານທາງກາຍະພາບທີ່ສຳຄັນທີ່ວັດແທກຄວາມນຳໄຟຟ້າຂອງແຜ່ນຊິລິໂຄນຜລຶກດຽວທີ່ຂັດເງົາ. ຄ່າຂອງມັນສະທ້ອນໃຫ້ເຫັນເຖິງປະສິດທິພາບການນຳໄຟຟ້າຂອງວັດສະດຸ. ຄວາມຕ້ານທານຕ່ຳເທົ່າໃດ, ຄວາມນຳໄຟຟ້າຂອງແຜ່ນຊິລິໂຄນກໍ່ຈະດີຂຶ້ນ; ໃນທາງກັບກັນ, ຄວາມຕ້ານທານສູງເທົ່າໃດ, ຄວາມນຳໄຟຟ້າກໍ່ຈະບໍ່ດີເທົ່ານັ້ນ. ຄວາມຕ້ານທານຂອງແຜ່ນຊິລິໂຄນແມ່ນຖືກກຳນົດໂດຍຄຸນສົມບັດຂອງວັດສະດຸທີ່ມີຢູ່, ແລະອຸນຫະພູມກໍ່ມີຜົນກະທົບຢ່າງຫຼວງຫຼາຍເຊັ່ນກັນ. ໂດຍທົ່ວໄປ, ຄວາມຕ້ານທານຂອງແຜ່ນຊິລິໂຄນຈະເພີ່ມຂຶ້ນຕາມອຸນຫະພູມ. ໃນການນຳໃຊ້ຕົວຈິງ, ອຸປະກອນເອເລັກໂຕຣນິກຂະໜາດນ້ອຍທີ່ແຕກຕ່າງກັນມີຄວາມຕ້ອງການຄວາມຕ້ານທານທີ່ແຕກຕ່າງກັນສຳລັບແຜ່ນຊິລິໂຄນ. ຕົວຢ່າງ, ແຜ່ນຊິລິໂຄນທີ່ໃຊ້ໃນການຜະລິດວົງຈອນລວມຕ້ອງການການຄວບຄຸມຄວາມຕ້ານທານທີ່ຊັດເຈນເພື່ອຮັບປະກັນປະສິດທິພາບຂອງອຸປະກອນທີ່ໝັ້ນຄົງແລະເຊື່ອຖືໄດ້.

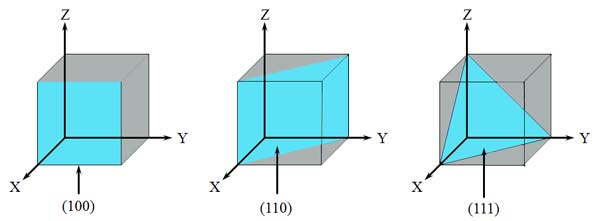

ທິດທາງ: ທິດທາງຜລຶກຂອງແຜ່ນເວເຟີສະແດງເຖິງທິດທາງຜລຶກຂອງໂຄງຊິລິກອນ, ໂດຍປົກກະຕິແລ້ວຈະລະບຸໄວ້ໂດຍດັດຊະນີ Miller ເຊັ່ນ (100), (110), (111), ແລະອື່ນໆ. ທິດທາງຜລຶກທີ່ແຕກຕ່າງກັນມີຄຸນສົມບັດທາງກາຍະພາບທີ່ແຕກຕ່າງກັນ, ເຊັ່ນ: ຄວາມໜາແໜ້ນຂອງເສັ້ນ, ເຊິ່ງແຕກຕ່າງກັນໄປຕາມທິດທາງ. ຄວາມແຕກຕ່າງນີ້ສາມາດສົ່ງຜົນກະທົບຕໍ່ປະສິດທິພາບຂອງແຜ່ນເວເຟີໃນຂັ້ນຕອນການປະມວນຜົນຕໍ່ມາ ແລະ ປະສິດທິພາບສຸດທ້າຍຂອງອຸປະກອນໄມໂຄຣເອເລັກໂຕຣນິກ. ໃນຂະບວນການຜະລິດ, ການເລືອກແຜ່ນເວເຟີຊິລິກອນທີ່ມີທິດທາງທີ່ເໝາະສົມສຳລັບຄວາມຕ້ອງການຂອງອຸປະກອນທີ່ແຕກຕ່າງກັນສາມາດເພີ່ມປະສິດທິພາບຂອງອຸປະກອນ, ປັບປຸງປະສິດທິພາບການຜະລິດ, ແລະ ເສີມຂະຫຍາຍຄຸນນະພາບຜະລິດຕະພັນ.

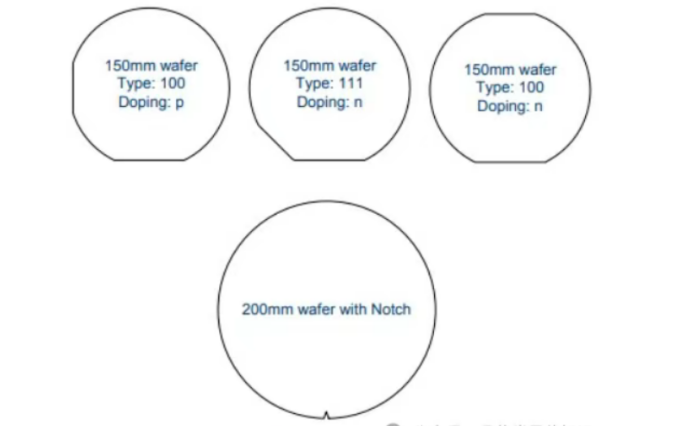

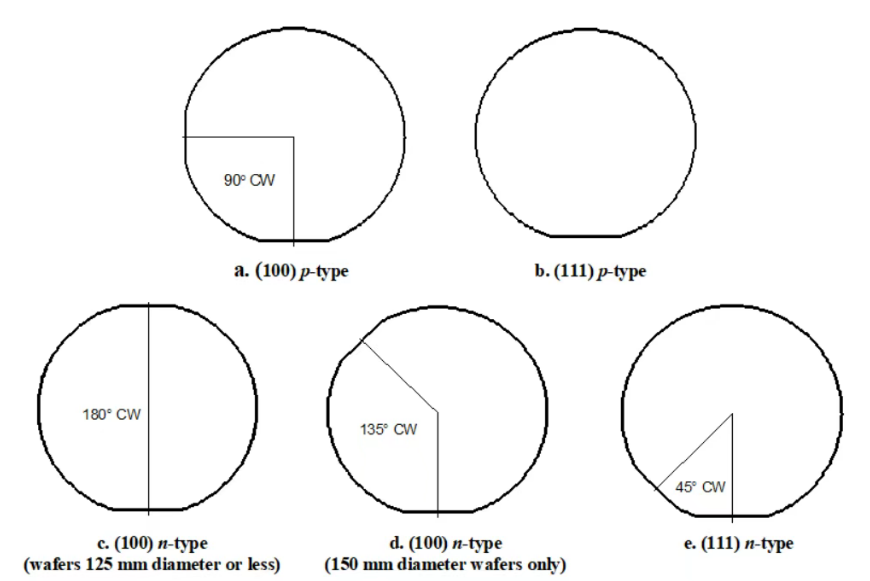

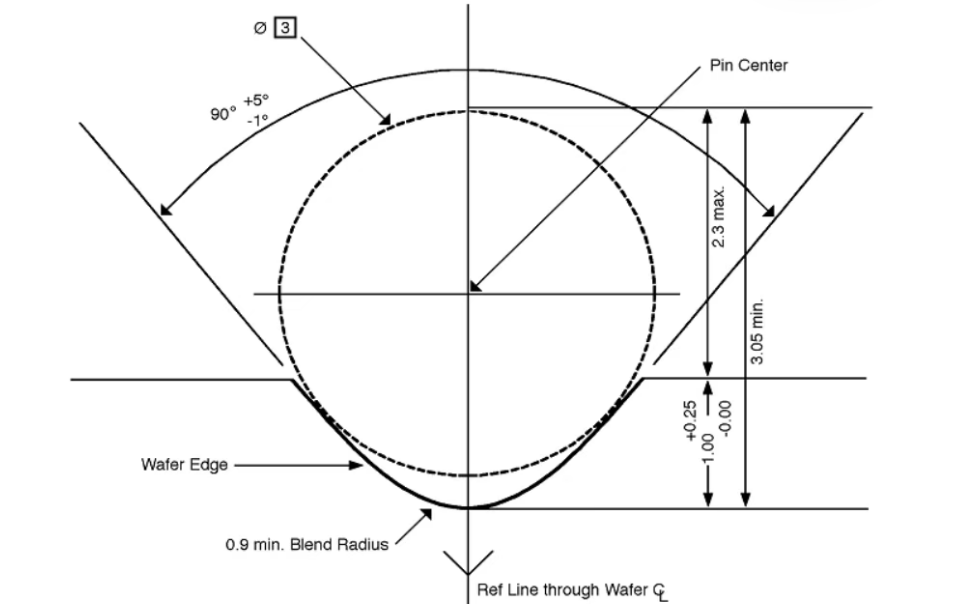

ຮາບພຽງ/ຮອຍບิ่น: ຂອບຮາບພຽງ (ຮາບພຽງ) ຫຼື ຮອຍບิ่นຮູບຕົວ V (ຮອຍບิ่น) ເທິງເສັ້ນຮອບວົງຂອງແຜ່ນຊິລິໂຄນມີບົດບາດສຳຄັນໃນການຈັດລຽງທິດທາງຂອງຜລຶກ ແລະ ເປັນຕົວລະບຸທີ່ສຳຄັນໃນການຜະລິດ ແລະ ການປຸງແຕ່ງແຜ່ນ. ແຜ່ນທີ່ມີເສັ້ນຜ່າສູນກາງແຕກຕ່າງກັນສອດຄ່ອງກັບມາດຕະຖານທີ່ແຕກຕ່າງກັນສຳລັບຄວາມຍາວຂອງແຜ່ນຮາບພຽງ ຫຼື ຮອຍບิ่น. ຂອບການຈັດລຽງຖືກຈັດປະເພດເປັນແຜ່ນຮາບພຽງຫຼັກ ແລະ ແຜ່ນຮາບພຽງສຳຮອງ. ແຜ່ນຮາບພຽງຫຼັກສ່ວນໃຫຍ່ແມ່ນໃຊ້ເພື່ອກຳນົດທິດທາງຂອງຜລຶກພື້ນຖານ ແລະ ເອກະສານອ້າງອີງການປະມວນຜົນຂອງແຜ່ນ, ໃນຂະນະທີ່ແຜ່ນຮາບພຽງສຳຮອງຍັງຊ່ວຍໃນການຈັດລຽງ ແລະ ການປະມວນຜົນທີ່ຊັດເຈນ, ຮັບປະກັນການເຮັດວຽກທີ່ຖືກຕ້ອງ ແລະ ຄວາມສອດຄ່ອງຂອງແຜ່ນຕະຫຼອດສາຍການຜະລິດ.

ຄວາມໜາ: ຄວາມໜາຂອງເວເຟີໂດຍທົ່ວໄປແມ່ນລະບຸໄວ້ເປັນໄມໂຄຣແມັດ (μm), ໂດຍມີຄວາມໜາທົ່ວໄປຢູ່ໃນລະຫວ່າງ 100μm ແລະ 1000μm. ເວເຟີທີ່ມີຄວາມໜາແຕກຕ່າງກັນແມ່ນເໝາະສົມກັບອຸປະກອນໄມໂຄຣເອເລັກໂຕຣນິກປະເພດຕ່າງໆ. ເວເຟີທີ່ບາງກວ່າ (ເຊັ່ນ: 100μm – 300μm) ມັກຖືກໃຊ້ສຳລັບການຜະລິດຊິບທີ່ຕ້ອງການການຄວບຄຸມຄວາມໜາຢ່າງເຂັ້ມງວດ, ຫຼຸດຜ່ອນຂະໜາດ ແລະ ນ້ຳໜັກຂອງຊິບ ແລະ ເພີ່ມຄວາມໜາແໜ້ນຂອງການເຊື່ອມໂຍງ. ເວເຟີທີ່ໜາກວ່າ (ເຊັ່ນ: 500μm – 1000μm) ຖືກນຳໃຊ້ຢ່າງກວ້າງຂວາງໃນອຸປະກອນທີ່ຕ້ອງການຄວາມແຂງແຮງທາງກົນຈັກທີ່ສູງກວ່າ, ເຊັ່ນ: ອຸປະກອນເຄິ່ງຕົວນຳພະລັງງານ, ເພື່ອຮັບປະກັນຄວາມໝັ້ນຄົງໃນລະຫວ່າງການປະຕິບັດງານ.

ຄວາມຫຍາບຂອງພື້ນຜິວ: ຄວາມຫຍາບຂອງພື້ນຜິວແມ່ນໜຶ່ງໃນຕົວກໍານົດຫຼັກສໍາລັບການປະເມີນຄຸນນະພາບຂອງແຜ່ນເວເຟີ, ເພາະມັນມີຜົນກະທົບໂດຍກົງຕໍ່ການຍຶດຕິດລະຫວ່າງແຜ່ນເວເຟີ ແລະ ວັດສະດຸຟິມບາງທີ່ຖອກລົງມາ, ເຊັ່ນດຽວກັນກັບປະສິດທິພາບທາງໄຟຟ້າຂອງອຸປະກອນ. ມັນມັກຈະສະແດງອອກເປັນຄວາມຫຍາບຂອງຄ່າສະເລ່ຍຮາກ (RMS) (ເປັນ nm). ຄວາມຫຍາບຂອງພື້ນຜິວທີ່ຕ່ຳກວ່າໝາຍຄວາມວ່າພື້ນຜິວແຜ່ນເວເຟີລຽບກວ່າ, ເຊິ່ງຊ່ວຍຫຼຸດຜ່ອນປະກົດການຕ່າງໆເຊັ່ນ: ການກະແຈກກະຈາຍຂອງເອເລັກຕຣອນ ແລະ ປັບປຸງປະສິດທິພາບ ແລະ ຄວາມໜ້າເຊື່ອຖືຂອງອຸປະກອນ. ໃນຂະບວນການຜະລິດເຄິ່ງຕົວນຳທີ່ກ້າວໜ້າ, ຄວາມຕ້ອງການຄວາມຫຍາບຂອງພື້ນຜິວກຳລັງມີຄວາມເຂັ້ມງວດເພີ່ມຂຶ້ນ, ໂດຍສະເພາະສຳລັບການຜະລິດວົງຈອນປະສົມປະສານລະດັບສູງ, ບ່ອນທີ່ຄວາມຫຍາບຂອງພື້ນຜິວຕ້ອງຖືກຄວບຄຸມໃຫ້ຢູ່ໃນລະດັບສອງສາມນາໂນແມັດ ຫຼື ຕ່ຳກວ່າ.

ການປ່ຽນແປງຄວາມໜາທັງໝົດ (TTV): ການປ່ຽນແປງຄວາມໜາທັງໝົດໝາຍເຖິງຄວາມແຕກຕ່າງລະຫວ່າງຄວາມໜາສູງສຸດ ແລະ ຕໍ່າສຸດທີ່ວັດແທກໄດ້ຢູ່ຫຼາຍຈຸດເທິງໜ້າແຜ່ນເວເຟີ, ໂດຍປົກກະຕິແລ້ວຈະສະແດງເປັນ μm. TTV ສູງອາດຈະນໍາໄປສູ່ຄວາມຜິດປົກກະຕິໃນຂະບວນການຕ່າງໆເຊັ່ນ: ການສ້າງຮູບດ້ວຍແສງ ແລະ ການແກະສະຫຼັກ, ເຊິ່ງສົ່ງຜົນກະທົບຕໍ່ຄວາມສອດຄ່ອງຂອງປະສິດທິພາບ ແລະ ຜົນຜະລິດຂອງອຸປະກອນ. ດັ່ງນັ້ນ, ການຄວບຄຸມ TTV ໃນລະຫວ່າງການຜະລິດແຜ່ນເວເຟີແມ່ນຂັ້ນຕອນທີ່ສໍາຄັນໃນການຮັບປະກັນຄຸນນະພາບຂອງຜະລິດຕະພັນ. ສໍາລັບການຜະລິດອຸປະກອນເອເລັກໂຕຣນິກທີ່ມີຄວາມແມ່ນຍໍາສູງ, TTV ໂດຍປົກກະຕິແລ້ວຈະຕ້ອງຢູ່ພາຍໃນສອງສາມໄມໂຄຣແມັດ.

ຄວາມໂຄ້ງ: ຄວາມໂຄ້ງໝາຍເຖິງຄວາມບ່ຽງເບນລະຫວ່າງໜ້າຜິວແຜ່ນເວເຟີ ແລະ ພື້ນຮາບພຽງທີ່ເໝາະສົມ, ໂດຍປົກກະຕິແລ້ວວັດແທກເປັນ μm. ແຜ່ນເວເຟີທີ່ມີການໂຄ້ງຫຼາຍເກີນໄປອາດຈະແຕກຫັກ ຫຼື ປະສົບກັບຄວາມກົດດັນທີ່ບໍ່ສະເໝີພາບໃນລະຫວ່າງການປຸງແຕ່ງຕໍ່ມາ, ສົ່ງຜົນກະທົບຕໍ່ປະສິດທິພາບການຜະລິດ ແລະ ຄຸນນະພາບຂອງຜະລິດຕະພັນ. ໂດຍສະເພາະໃນຂະບວນການທີ່ຕ້ອງການຄວາມຮາບພຽງສູງ, ເຊັ່ນ: ການພິມດ້ວຍແສງ, ການໂຄ້ງຕ້ອງໄດ້ຮັບການຄວບຄຸມພາຍໃນຂອບເຂດສະເພາະເພື່ອຮັບປະກັນຄວາມຖືກຕ້ອງ ແລະ ຄວາມສອດຄ່ອງຂອງຮູບແບບການພິມດ້ວຍແສງ.

ການບິດງໍ: ການບິດງໍຊີ້ບອກເຖິງຄວາມບ່ຽງເບນລະຫວ່າງໜ້າຜິວເວເຟີ ແລະ ຮູບຮ່າງກົມທີ່ເໝາະສົມ, ເຊິ່ງວັດແທກເປັນ μm. ຄ້າຍຄືກັບການໂຄ້ງ, ການບິດງໍເປັນຕົວຊີ້ບອກທີ່ສຳຄັນຂອງຄວາມຮາບພຽງຂອງເວເຟີ. ການບິດງໍຫຼາຍເກີນໄປບໍ່ພຽງແຕ່ສົ່ງຜົນກະທົບຕໍ່ຄວາມຖືກຕ້ອງຂອງການວາງຂອງເວເຟີໃນອຸປະກອນປະມວນຜົນເທົ່ານັ້ນ, ແຕ່ຍັງສາມາດເຮັດໃຫ້ເກີດບັນຫາໃນລະຫວ່າງຂະບວນການຫຸ້ມຫໍ່ຊິບ, ເຊັ່ນ: ການຍຶດຕິດທີ່ບໍ່ດີລະຫວ່າງຊິບ ແລະ ວັດສະດຸຫຸ້ມຫໍ່, ເຊິ່ງສົ່ງຜົນກະທົບຕໍ່ຄວາມໜ້າເຊື່ອຖືຂອງອຸປະກອນ. ໃນການຜະລິດເຄິ່ງຕົວນຳລະດັບສູງ, ຄວາມຕ້ອງການການບິດງໍກຳລັງມີຄວາມເຂັ້ມງວດຫຼາຍຂຶ້ນເພື່ອຕອບສະໜອງຄວາມຕ້ອງການຂອງຂະບວນການຜະລິດຊິບ ແລະ ການຫຸ້ມຫໍ່ທີ່ກ້າວໜ້າ.

ໂປຣໄຟລ໌ຂອບ: ໂປຣໄຟລ໌ຂອບຂອງແຜ່ນເວເຟີແມ່ນມີຄວາມສຳຄັນຫຼາຍສຳລັບການປະມວນຜົນ ແລະ ການຈັດການຕໍ່ໄປ. ໂດຍປົກກະຕິແລ້ວມັນຖືກລະບຸໄວ້ໂດຍເຂດຍົກເວັ້ນຂອບ (EEZ), ເຊິ່ງກຳນົດໄລຍະຫ່າງຈາກຂອບແຜ່ນເວເຟີທີ່ບໍ່ອະນຸຍາດໃຫ້ມີການປະມວນຜົນ. ໂປຣໄຟລ໌ຂອບທີ່ອອກແບບຢ່າງຖືກຕ້ອງ ແລະ ການຄວບຄຸມ EEZ ທີ່ຊັດເຈນຊ່ວຍຫຼີກເວັ້ນຂໍ້ບົກຜ່ອງຂອງຂອບ, ຄວາມເຂັ້ມຂຸ້ນຂອງຄວາມກົດດັນ, ແລະ ບັນຫາອື່ນໆໃນລະຫວ່າງການປະມວນຜົນ, ປັບປຸງຄຸນນະພາບ ແລະ ຜົນຜະລິດຂອງແຜ່ນເວເຟີໂດຍລວມ. ໃນຂະບວນການຜະລິດທີ່ກ້າວໜ້າບາງຢ່າງ, ຄວາມແມ່ນຍຳຂອງໂປຣໄຟລ໌ຂອບແມ່ນຕ້ອງຢູ່ໃນລະດັບຊັບໄມຄຣອນ.

ການນັບຈຳນວນອະນຸພາກ: ການແຈກຢາຍຈຳນວນ ແລະ ຂະໜາດຂອງອະນຸພາກເທິງໜ້າເວເຟີມີຜົນກະທົບຢ່າງຫຼວງຫຼາຍຕໍ່ປະສິດທິພາບຂອງອຸປະກອນໄມໂຄຣເອເລັກໂຕຣນິກ. ອະນຸພາກທີ່ຫຼາຍເກີນໄປ ຫຼື ໃຫຍ່ອາດນຳໄປສູ່ຄວາມລົ້ມເຫຼວຂອງອຸປະກອນ, ເຊັ່ນ: ການລັດວົງຈອນ ຫຼື ການຮົ່ວໄຫຼ, ເຊິ່ງເຮັດໃຫ້ຜົນຜະລິດຜະລິດຕະພັນຫຼຸດລົງ. ດັ່ງນັ້ນ, ການນັບອະນຸພາກມັກຈະຖືກວັດແທກໂດຍການນັບອະນຸພາກຕໍ່ໜ່ວຍພື້ນທີ່, ເຊັ່ນ: ຈຳນວນອະນຸພາກທີ່ໃຫຍ່ກວ່າ 0.3μm. ການຄວບຄຸມຢ່າງເຂັ້ມງວດຂອງການນັບອະນຸພາກໃນລະຫວ່າງການຜະລິດເວເຟີແມ່ນມາດຕະການທີ່ສຳຄັນເພື່ອຮັບປະກັນຄຸນນະພາບຂອງຜະລິດຕະພັນ. ເຕັກໂນໂລຊີການທຳຄວາມສະອາດທີ່ກ້າວໜ້າ ແລະ ສະພາບແວດລ້ອມການຜະລິດທີ່ສະອາດແມ່ນໃຊ້ເພື່ອຫຼຸດຜ່ອນການປົນເປື້ອນຂອງອະນຸພາກເທິງໜ້າເວເຟີ.

![]()

![]()

![]()

![]()

![]()

ການຜະລິດທີ່ກ່ຽວຂ້ອງ

ເວເຟີຊິລິໂຄນຜລຶກດຽວ ປະເພດຊັ້ນ Si N/P ເວເຟີຊິລິໂຄນຄາໄບທາງເລືອກ

ເວເຟີ FZ CZ Si ມີໃນສະຕັອກ ເວເຟີຊິລິໂຄນຂະໜາດ 12 ນິ້ວ Prime ຫຼື Test

ເວລາໂພສ: ວັນທີ 18 ເມສາ 2025