ບົດຄັດຫຍໍ້ຂອງເວເຟີ SiC

ເວເຟີຊິລິກອນຄາໄບ (SiC)ໄດ້ກາຍເປັນວັດສະດຸພື້ນຖານທີ່ເລືອກສຳລັບເອເລັກໂຕຣນິກພະລັງງານສູງ, ຄວາມຖີ່ສູງ, ແລະອຸນຫະພູມສູງໃນທົ່ວຂະແໜງຍານຍົນ, ພະລັງງານທົດແທນ, ແລະການບິນອະວະກາດ. ຜະລິດຕະພັນຂອງພວກເຮົາກວມເອົາ polytypes ທີ່ສຳຄັນ ແລະ ແຜນການເສີມ — 4H ທີ່ມີທາດໄນໂຕຣເຈນ (4H-N), ເຄິ່ງສນວນທີ່ມີຄວາມບໍລິສຸດສູງ (HPSI), 3C ທີ່ມີທາດໄນໂຕຣເຈນ (3C-N), ແລະ p-type 4H/6H (4H/6H-P) — ສະເໜີໃນສາມຊັ້ນຄຸນນະພາບຄື: PRIME (ຂັດເງົາເຕັມທີ່, ວັດສະດຸພື້ນຖານລະດັບອຸປະກອນ), DUMMY (ຂັດ ຫຼື ບໍ່ຂັດເງົາສຳລັບການທົດລອງຂະບວນການ), ແລະ RESEARCH (ຊັ້ນ epi ທີ່ກຳນົດເອງ ແລະ ໂປຣໄຟລ໌ເສີມສຳລັບການຄົ້ນຄວ້າ ແລະ ພັດທະນາ). ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີມີຂະໜາດ 2″, 4″, 6″, 8″, ແລະ 12″ ເພື່ອໃຫ້ເໝາະສົມກັບທັງເຄື່ອງມືແບບດັ້ງເດີມ ແລະ ໂຮງງານຜະລິດທີ່ກ້າວໜ້າ. ພວກເຮົາຍັງສະໜອງລູກບານ monocrystalline ແລະ ເມັດແກ້ວທີ່ມີທິດທາງທີ່ຊັດເຈນເພື່ອສະໜັບສະໜູນການເຕີບໂຕຂອງຜລຶກພາຍໃນ.

ເວເຟີ 4H-N ຂອງພວກເຮົາມີຄວາມໜາແໜ້ນຂອງຕົວນຳຕັ້ງແຕ່ 1×10¹⁶ ຫາ 1×10¹⁹ cm⁻³ ແລະ ຄວາມຕ້ານທານ 0.01–10 Ω·cm, ສະໜອງການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນ ແລະ ສະໜາມການແຕກຫັກທີ່ດີເລີດສູງກວ່າ 2 MV/cm—ເໝາະສຳລັບໄດໂອດ Schottky, MOSFETs, ແລະ JFETs. ຊັບສະເຕຣດ HPSI ມີຄວາມຕ້ານທານເກີນ 1×10¹² Ω·cm ດ້ວຍຄວາມໜາແໜ້ນຂອງທໍ່ຂະໜາດນ້ອຍກວ່າ 0.1 cm⁻², ຮັບປະກັນການຮົ່ວໄຫຼໜ້ອຍທີ່ສຸດສຳລັບອຸປະກອນ RF ແລະ ໄມໂຄເວຟ. Cubic 3C-N, ມີໃຫ້ໃນຮູບແບບ 2″ ແລະ 4″, ຊ່ວຍໃຫ້ heteroepitaxy ໃນຊິລິກອນ ແລະ ຮອງຮັບການນຳໃຊ້ photonic ແລະ MEMS ແບບໃໝ່. ເວເຟີປະເພດ P-type 4H/6H-P, ເສີມດ້ວຍອາລູມີນຽມເຖິງ 1×10¹⁶–5×10¹⁸ cm⁻³, ອຳນວຍຄວາມສະດວກໃຫ້ແກ່ສະຖາປັດຕະຍະກຳອຸປະກອນທີ່ສົມບູນ.

ເວເຟີ SiC, ເວເຟີ PRIME ໄດ້ຮັບການຂັດເງົາທາງເຄມີ-ກົນຈັກຈົນມີຄວາມຫຍາບຂອງພື້ນຜິວ RMS <0.2 nm, ການປ່ຽນແປງຄວາມໜາທັງໝົດຕໍ່າກວ່າ 3 µm, ແລະ ຄວາມໂຄ້ງ <10 µm. ຊັ້ນຮອງພື້ນ DUMMY ເລັ່ງການທົດສອບການປະກອບ ແລະ ການຫຸ້ມຫໍ່, ໃນຂະນະທີ່ເວເຟີ RESEARCH ມີຄວາມໜາຂອງຊັ້ນ epi 2–30 µm ແລະ ການເສີມທີ່ເຮັດຕາມຄວາມຕ້ອງການ. ຜະລິດຕະພັນທັງໝົດໄດ້ຮັບການຮັບຮອງໂດຍການກະຈາຍລັງສີ X (ເສັ້ນໂຄ້ງການໂຍກ <30 arcsec) ແລະ ການວິເຄາະດ້ວຍແສງ Raman, ພ້ອມດ້ວຍການທົດສອບທາງໄຟຟ້າ—ການວັດແທກ Hall, ການວິເຄາະໂປຣໄຟລ໌ C–V, ແລະ ການສະແກນ micropipe—ຮັບປະກັນການປະຕິບັດຕາມ JEDEC ແລະ SEMI.

ລູກບານທີ່ມີເສັ້ນຜ່າສູນກາງເຖິງ 150 ມມ ຖືກປູກຜ່ານ PVT ແລະ CVD ດ້ວຍຄວາມໜາແໜ້ນຂອງການເຄື່ອນທີ່ຕ່ຳກວ່າ 1×10³ cm⁻² ແລະ ຈຳນວນໄມໂຄຣທໍ່ຕ່ຳ. ຜລຶກເມັດຖືກຕັດພາຍໃນ 0.1° ຂອງແກນ c ເພື່ອຮັບປະກັນການເຕີບໃຫຍ່ທີ່ສາມາດສືບພັນໄດ້ ແລະ ຜົນຜະລິດສູງໃນການຊອຍ.

ໂດຍການລວມເອົາຫຼາຍຊະນິດຂອງໂພລີໄທບ໌, ການປ່ຽນແປງຂອງສານເສີມ, ຊັ້ນຄຸນນະພາບ, ຂະໜາດແຜ່ນ SiC, ແລະ ການຜະລິດລູກບານ ແລະ ເມັດແກ້ວພາຍໃນ, ແພລດຟອມພື້ນຖານ SiC ຂອງພວກເຮົາຈະປັບປຸງລະບົບຕ່ອງໂສ້ການສະໜອງໃຫ້ມີປະສິດທິພາບ ແລະ ເລັ່ງການພັດທະນາອຸປະກອນສຳລັບພາຫະນະໄຟຟ້າ, ຕາຂ່າຍໄຟຟ້າອັດສະລິຍະ, ແລະ ການນຳໃຊ້ໃນສະພາບແວດລ້ອມທີ່ຮຸນແຮງ.

ບົດຄັດຫຍໍ້ຂອງເວເຟີ SiC

ເວເຟີຊິລິກອນຄາໄບ (SiC)ໄດ້ກາຍເປັນວັດສະດຸ SiC ທີ່ຖືກເລືອກສຳລັບເອເລັກໂຕຣນິກພະລັງງານສູງ, ຄວາມຖີ່ສູງ, ແລະອຸນຫະພູມສູງໃນທົ່ວຂະແໜງຍານຍົນ, ພະລັງງານທົດແທນ, ແລະການບິນອະວະກາດ. ຜະລິດຕະພັນຂອງພວກເຮົາກວມເອົາ polytypes ທີ່ສຳຄັນ ແລະໂຄງການເສີມ — 4H ທີ່ເສີມໄນໂຕຣເຈນ (4H-N), ເຄິ່ງສນວນທີ່ມີຄວາມບໍລິສຸດສູງ (HPSI), 3C ທີ່ເສີມໄນໂຕຣເຈນ (3C-N), ແລະ p-type 4H/6H (4H/6H-P) — ສະເໜີໃນສາມເກຣດຄຸນນະພາບຄື: ເວເຟີ SiCPRIME (ຂັດເງົາຢ່າງສົມບູນ, ຊັ້ນວັດສະດຸລະດັບອຸປະກອນ), DUMMY (ຂັດ ຫຼື ບໍ່ຂັດເງົາສຳລັບການທົດລອງຂະບວນການ), ແລະ RESEARCH (ຊັ້ນ epi ທີ່ກຳນົດເອງ ແລະ ໂປຣໄຟລ໌ການເສີມສຳລັບ R&D). ເສັ້ນຜ່າສູນກາງຂອງແຜ່ນ SiC ມີຂະໜາດ 2 ນິ້ວ, 4 ນິ້ວ, 6 ນິ້ວ, 8 ນິ້ວ, ແລະ 12 ນິ້ວ ເພື່ອໃຫ້ເໝາະສົມກັບທັງເຄື່ອງມືແບບດັ້ງເດີມ ແລະ ໂຮງງານຜະລິດທີ່ກ້າວໜ້າ. ພວກເຮົາຍັງສະໜອງລູກບານ monocrystalline ແລະ ເມັດແກ້ວທີ່ມີທິດທາງທີ່ຊັດເຈນເພື່ອສະໜັບສະໜູນການເຕີບໂຕຂອງຜລຶກພາຍໃນ.

ເວເຟີ SiC 4H-N ຂອງພວກເຮົາມີຄວາມໜາແໜ້ນຂອງພາຫະນະຕັ້ງແຕ່ 1×10¹⁶ ຫາ 1×10¹⁹ cm⁻³ ແລະ ຄວາມຕ້ານທານ 0.01–10 Ω·cm, ສະໜອງການເຄື່ອນທີ່ຂອງເອເລັກຕຣອນ ແລະ ສະໜາມການແຕກຫັກທີ່ດີເລີດສູງກວ່າ 2 MV/cm—ເໝາະສຳລັບໄດໂອດ Schottky, MOSFETs, ແລະ JFETs. ຊັບສະເຕຣດ HPSI ເກີນຄວາມຕ້ານທານ 1×10¹² Ω·cm ດ້ວຍຄວາມໜາແໜ້ນຂອງທໍ່ຂະໜາດນ້ອຍກວ່າ 0.1 cm⁻², ຮັບປະກັນການຮົ່ວໄຫຼໜ້ອຍທີ່ສຸດສຳລັບອຸປະກອນ RF ແລະ ໄມໂຄເວຟ. Cubic 3C-N, ມີໃຫ້ໃນຮູບແບບ 2″ ແລະ 4″, ຊ່ວຍໃຫ້ heteroepitaxy ໃນຊິລິກອນ ແລະ ຮອງຮັບການນຳໃຊ້ photonic ແລະ MEMS ແບບໃໝ່. ເວເຟີ SiC ເວເຟີ P-type 4H/6H-P, ເສີມດ້ວຍອາລູມີນຽມເຖິງ 1×10¹⁶–5×10¹⁸ cm⁻³, ອຳນວຍຄວາມສະດວກໃຫ້ແກ່ສະຖາປັດຕະຍະກຳອຸປະກອນທີ່ສົມບູນ.

ເວເຟີ SiC PRIME ຜ່ານການຂັດເງົາທາງເຄມີ-ກົນຈັກຈົນເຖິງຄວາມຫຍາບຂອງພື້ນຜິວ RMS <0.2 nm, ການປ່ຽນແປງຄວາມໜາທັງໝົດຕໍ່າກວ່າ 3 µm, ແລະ ຄວາມໂຄ້ງ <10 µm. ຊັ້ນຮອງພື້ນ DUMMY ເລັ່ງການທົດສອບການປະກອບ ແລະ ການຫຸ້ມຫໍ່, ໃນຂະນະທີ່ເວເຟີ RESEARCH ມີຄວາມໜາຂອງຊັ້ນ epi 2–30 µm ແລະ ການເສີມທີ່ເຮັດຕາມຄວາມຕ້ອງການ. ຜະລິດຕະພັນທັງໝົດໄດ້ຮັບການຮັບຮອງໂດຍການກະຈາຍລັງສີ X (ເສັ້ນໂຄ້ງການໂຍກ <30 arcsec) ແລະ ການວິເຄາະແສງ Raman, ພ້ອມດ້ວຍການທົດສອບທາງໄຟຟ້າ—ການວັດແທກ Hall, ການວິເຄາະໂປຣໄຟລ໌ C–V, ແລະ ການສະແກນ micropipe—ຮັບປະກັນການປະຕິບັດຕາມ JEDEC ແລະ SEMI.

ລູກບານທີ່ມີເສັ້ນຜ່າສູນກາງເຖິງ 150 ມມ ຖືກປູກຜ່ານ PVT ແລະ CVD ດ້ວຍຄວາມໜາແໜ້ນຂອງການເຄື່ອນທີ່ຕ່ຳກວ່າ 1×10³ cm⁻² ແລະ ຈຳນວນໄມໂຄຣທໍ່ຕ່ຳ. ຜລຶກເມັດຖືກຕັດພາຍໃນ 0.1° ຂອງແກນ c ເພື່ອຮັບປະກັນການເຕີບໃຫຍ່ທີ່ສາມາດສືບພັນໄດ້ ແລະ ຜົນຜະລິດສູງໃນການຊອຍ.

ໂດຍການລວມເອົາຫຼາຍຊະນິດຂອງໂພລີໄທບ໌, ການປ່ຽນແປງຂອງສານເສີມ, ຊັ້ນຄຸນນະພາບ, ຂະໜາດແຜ່ນ SiC, ແລະ ການຜະລິດລູກບານ ແລະ ເມັດແກ້ວພາຍໃນ, ແພລດຟອມພື້ນຖານ SiC ຂອງພວກເຮົາຈະປັບປຸງລະບົບຕ່ອງໂສ້ການສະໜອງໃຫ້ມີປະສິດທິພາບ ແລະ ເລັ່ງການພັດທະນາອຸປະກອນສຳລັບພາຫະນະໄຟຟ້າ, ຕາຂ່າຍໄຟຟ້າອັດສະລິຍະ, ແລະ ການນຳໃຊ້ໃນສະພາບແວດລ້ອມທີ່ຮຸນແຮງ.

ແຜ່ນຂໍ້ມູນຂອງແຜ່ນເວເຟີ SiC ປະເພດ 4H-N ຂະໜາດ 6 ນິ້ວ

| ແຜ່ນຂໍ້ມູນເວເຟີ SiC ຂະໜາດ 6 ນິ້ວ | ||||

| ພາລາມິເຕີ | ພາລາມິເຕີຍ່ອຍ | ຊັ້ນ Z | ເກຣດ P | ຊັ້ນ D |

| ເສັ້ນຜ່າສູນກາງ | 149.5–150.0 ມມ | 149.5–150.0 ມມ | 149.5–150.0 ມມ | |

| ຄວາມໜາ | 4H‑N | 350 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 350 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | 350 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ຄວາມໜາ | 4H-SI | 500 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ນອກແກນ: 4.0° ໄປທາງ <11-20> ±0.5° (4H-N); ເທິງແກນ: <0001> ±0.5° (4H-SI) | ນອກແກນ: 4.0° ໄປທາງ <11-20> ±0.5° (4H-N); ເທິງແກນ: <0001> ±0.5° (4H-SI) | ນອກແກນ: 4.0° ໄປທາງ <11-20> ±0.5° (4H-N); ເທິງແກນ: <0001> ±0.5° (4H-SI) | |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | 4H‑N | ≤ 0.2 ຊມ⁻² | ≤ 2 ຊມ⁻² | ≤ 15 ຊມ⁻² |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ | 4H-SI | ≤ 1 ຊມ⁻² | ≤ 5 ຊມ⁻² | ≤ 15 ຊມ⁻² |

| ຄວາມຕ້ານທານ | 4H‑N | 0.015–0.024 Ω·ຊມ | 0.015–0.028 Ω·ຊມ | 0.015–0.028 Ω·ຊມ |

| ຄວາມຕ້ານທານ | 4H-SI | ≥ 1×10¹⁰ Ω·ຊມ | ≥ 1×10⁵ Ω·ຊມ | |

| ທິດທາງຮາບພຽງຫຼັກ | [10-10] ± 5.0° | [10-10] ± 5.0° | [10-10] ± 5.0° | |

| ຄວາມຍາວຮາບພຽງຫຼັກ | 4H‑N | 47.5 ມມ ± 2.0 ມມ | ||

| ຄວາມຍາວຮາບພຽງຫຼັກ | 4H-SI | ຮອຍບາດ | ||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | |||

| Warp/LTV/TTV/Bow | ≤2.5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| ຄວາມຫຍາບ | ພາສາໂປໂລຍ | Ra ≤ 1 ນາໂນແມັດ | ||

| ຄວາມຫຍາບ | ຊິມພີ | Ra ≤ 0.2 ນາໂນແມັດ | Ra ≤ 0.5 ນາໂນແມັດ | |

| ຮອຍແຕກຂອບ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤ 20 ມມ, ດ່ຽວ ≤ 2 ມມ | ||

| ແຜ່ນຫົກຫລ່ຽມ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 0.1% | ພື້ນທີ່ສະສົມ ≤ 1% | |

| ພື້ນທີ່ຫຼາຍຮູບແບບ | ບໍ່ມີ | ພື້ນທີ່ສະສົມ ≤ 3% | ພື້ນທີ່ສະສົມ ≤ 3% | |

| ການລວມຕົວຂອງຄາບອນ | ພື້ນທີ່ສະສົມ ≤ 0.05% | ພື້ນທີ່ສະສົມ ≤ 3% | ||

| ຮອຍຂີດຂ່ວນເທິງໜ້າດິນ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤ 1 × ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | ||

| ຊິບຂອບ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥ 0.2 ມມ | ສູງສຸດ 7 ຊິບ, ≤ 1 ມມ ແຕ່ລະອັນ | ||

| TSD (ການເຄື່ອນທີ່ຂອງສະກູແບບເກຍ) | ≤ 500 ຊມ⁻² | ບໍ່ມີຂໍ້ມູນ | ||

| BPD (ການເຄື່ອນທີ່ຂອງລະນາບພື້ນຖານ) | ≤ 1000 ຊມ⁻² | ບໍ່ມີຂໍ້ມູນ | ||

| ການປົນເປື້ອນພື້ນຜິວ | ບໍ່ມີ | |||

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | |

ແຜ່ນຂໍ້ມູນຂອງແຜ່ນເວເຟີ SiC ປະເພດ 4H-N ຂະໜາດ 4 ນິ້ວ

| ແຜ່ນຂໍ້ມູນຂອງແຜ່ນ SiC 4 ນິ້ວ | |||

| ພາລາມິເຕີ | ການຜະລິດ MPD ເປັນສູນ | ຊັ້ນຜະລິດມາດຕະຖານ (ຊັ້ນ P) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ | 99.5 ມມ–100.0 ມມ | ||

| ຄວາມໜາ (4H-N) | 350 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 350 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | |

| ຄວາມໜາ (4H-Si) | 500 ໄມໂຄຣມ ± 15 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ນອກແກນ: 4.0° ໄປທາງ <1120> ±0.5° ສຳລັບ 4H-N; ເທິງແກນ: <0001> ±0.5° ສຳລັບ 4H-Si | ||

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ (4H-N) | ≤0.2 ຊມ⁻² | ≤2 ຊມ⁻² | ≤15 ຊມ⁻² |

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ (4H-Si) | ≤1 ຊມ⁻² | ≤5 ຊມ⁻² | ≤15 ຊມ⁻² |

| ຄວາມຕ້ານທານ (4H-N) | 0.015–0.024 Ω·ຊມ | 0.015–0.028 Ω·ຊມ | |

| ຄວາມຕ້ານທານ (4H-Si) | ≥1E10 Ω·ຊມ | ≥1E5 Ω·ຊມ | |

| ທິດທາງຮາບພຽງຫຼັກ | [10-10] ±5.0° | ||

| ຄວາມຍາວຮາບພຽງຫຼັກ | 32.5 ມມ ±2.0 ມມ | ||

| ຄວາມຍາວຮາບພຽງຂັ້ນສອງ | 18.0 ມມ ±2.0 ມມ | ||

| ທິດທາງຮາບພຽງຂັ້ນສອງ | ຊິລິໂຄນຫັນໜ້າຂຶ້ນ: 90° CW ຈາກພື້ນຮາບພຽງ ±5.0° | ||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | ||

| LTV/TTV/Bow Warp | ≤2.5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| ຄວາມຫຍາບ | ໂປໂລຍ Ra ≤1 nm; CMP Ra ≤0.2 nm | Ra ≤0.5 ນາໂນແມັດ | |

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ບໍ່ມີ | ຄວາມຍາວລວມ ≤10 ມມ; ຄວາມຍາວດ່ຽວ ≤2 ມມ |

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.1% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ພື້ນທີ່ສະສົມ ≤3% | |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤3% | |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤1 ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥0.2 ມມ | ອະນຸຍາດໃຫ້ 5 ອັນ, ≤1 ມມ ແຕ່ລະອັນ | |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ||

| ການເຄື່ອນທີ່ຂອງສະກູເກຍ | ≤500 ຊມ⁻² | ບໍ່ມີຂໍ້ມູນ | |

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ |

ແຜ່ນຂໍ້ມູນຂອງເວເຟີ SiC ປະເພດ HPSI 4 ນິ້ວ

| ແຜ່ນຂໍ້ມູນຂອງເວເຟີ SiC ປະເພດ HPSI 4 ນິ້ວ | |||

| ພາລາມິເຕີ | ຊັ້ນຜະລິດ MPD ເປັນສູນ (ຊັ້ນ Z) | ຊັ້ນຜະລິດມາດຕະຖານ (ຊັ້ນ P) | ຊັ້ນ D (ຊັ້ນ D) |

| ເສັ້ນຜ່າສູນກາງ | 99.5–100.0 ມມ | ||

| ຄວາມໜາ (4H-Si) | 500 ໄມໂຄຣມ ± 20 ໄມໂຄຣມ | 500 ໄມໂຄຣມ ± 25 ໄມໂຄຣມ | |

| ທິດທາງຂອງແຜ່ນເວເຟີ | ນອກແກນ: 4.0° ໄປທາງ <11-20> ±0.5° ສຳລັບ 4H-N; ເທິງແກນ: <0001> ±0.5° ສຳລັບ 4H-Si | ||

| ຄວາມໜາແໜ້ນຂອງທໍ່ນ້ອຍ (4H-Si) | ≤1 ຊມ⁻² | ≤5 ຊມ⁻² | ≤15 ຊມ⁻² |

| ຄວາມຕ້ານທານ (4H-Si) | ≥1E9 Ω·ຊມ | ≥1E5 Ω·ຊມ | |

| ທິດທາງຮາບພຽງຫຼັກ | (10-10) ±5.0° | ||

| ຄວາມຍາວຮາບພຽງຫຼັກ | 32.5 ມມ ±2.0 ມມ | ||

| ຄວາມຍາວຮາບພຽງຂັ້ນສອງ | 18.0 ມມ ±2.0 ມມ | ||

| ທິດທາງຮາບພຽງຂັ້ນສອງ | ຊິລິໂຄນຫັນໜ້າຂຶ້ນ: 90° CW ຈາກພື້ນຮາບພຽງ ±5.0° | ||

| ການຍົກເວັ້ນຂອບ | 3 ມມ | ||

| LTV/TTV/Bow Warp | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| ຄວາມຫຍາບ (ໜ້າ C) | ພາສາໂປໂລຍ | Ra ≤1 ນາໂນແມັດ | |

| ຄວາມຫຍາບ (ໜ້າ Si) | ຊິມພີ | Ra ≤0.2 ນາໂນແມັດ | Ra ≤0.5 ນາໂນແມັດ |

| ຮອຍແຕກຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ຄວາມຍາວລວມ ≤10 ມມ; ຄວາມຍາວດ່ຽວ ≤2 ມມ | |

| ແຜ່ນ Hex ໂດຍແສງຄວາມເຂັ້ມສູງ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤0.1% |

| ພື້ນທີ່ Polytype ໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ພື້ນທີ່ສະສົມ ≤3% | |

| ການລວມຕົວຂອງຄາບອນທີ່ເບິ່ງເຫັນໄດ້ | ພື້ນທີ່ສະສົມ ≤0.05% | ພື້ນທີ່ສະສົມ ≤3% | |

| ຮອຍຂີດຂ່ວນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ຄວາມຍາວສະສົມ ≤1 ເສັ້ນຜ່າສູນກາງແຜ່ນເວເຟີ | |

| ຊິບຂອບໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ອະນຸຍາດໃຫ້ມີຄວາມກວ້າງ ແລະ ຄວາມເລິກ ≥0.2 ມມ | ອະນຸຍາດໃຫ້ 5 ອັນ, ≤1 ມມ ແຕ່ລະອັນ | |

| ການປົນເປື້ອນພື້ນຜິວຊິລິໂຄນໂດຍແສງຄວາມເຂັ້ມສູງ | ບໍ່ມີ | ບໍ່ມີ | |

| ການເຄື່ອນທີ່ຂອງສະກູທີ່ເຈາະເກຍ | ≤500 ຊມ⁻² | ບໍ່ມີຂໍ້ມູນ | |

| ການຫຸ້ມຫໍ່ | ເທບຫຼາຍແຜ່ນ ຫຼື ພາຊະນະແຜ່ນດຽວ | ||

ຄໍາຮ້ອງສະຫມັກຂອງແຜ່ນຊີຊີກ

-

ໂມດູນພະລັງງານ SiC Wafer ສຳລັບອິນເວີເຕີ EV

MOSFETs ແລະ ໄດໂອດທີ່ອີງໃສ່ແຜ່ນເວເຟີ SiC ທີ່ສ້າງຂຶ້ນເທິງຊັ້ນວາງແຜ່ນເວເຟີ SiC ທີ່ມີຄຸນນະພາບສູງສົ່ງຜົນໃຫ້ການສູນເສຍການສະຫຼັບທີ່ຕໍ່າຫຼາຍ. ໂດຍການນຳໃຊ້ເຕັກໂນໂລຊີແຜ່ນເວເຟີ SiC, ໂມດູນພະລັງງານເຫຼົ່ານີ້ເຮັດວຽກຢູ່ທີ່ແຮງດັນ ແລະ ອຸນຫະພູມທີ່ສູງຂຶ້ນ, ເຮັດໃຫ້ຕົວປ່ຽນແຮງດຶງມີປະສິດທິພາບຫຼາຍຂຶ້ນ. ການລວມເອົາແຜ່ນເວເຟີ SiC ເຂົ້າໃນຂັ້ນຕອນພະລັງງານຊ່ວຍຫຼຸດຜ່ອນຄວາມຕ້ອງການດ້ານການເຮັດໃຫ້ເຢັນ ແລະ ຮອຍຕີນ, ສະແດງໃຫ້ເຫັນເຖິງທ່າແຮງຢ່າງເຕັມທີ່ຂອງນະວັດຕະກໍາແຜ່ນເວເຟີ SiC. -

ອຸປະກອນ RF ຄວາມຖີ່ສູງ ແລະ 5G ໃນ SiC Wafer

ເຄື່ອງຂະຫຍາຍສັນຍານ RF ແລະສະວິດທີ່ຜະລິດຢູ່ເທິງແພລດຟອມເວເຟີ SiC ເຄິ່ງສນວນສະແດງໃຫ້ເຫັນເຖິງຄວາມນຳຄວາມຮ້ອນ ແລະແຮງດັນໄຟຟ້າທີ່ດີກວ່າ. ຊັ້ນຮອງເວເຟີ SiC ຫຼຸດຜ່ອນການສູນເສຍໄຟຟ້າທີ່ຄວາມຖີ່ GHz, ໃນຂະນະທີ່ຄວາມແຂງແຮງຂອງວັດສະດຸເວເຟີ SiC ຊ່ວຍໃຫ້ການເຮັດວຽກທີ່ໝັ້ນຄົງພາຍໃຕ້ສະພາບພະລັງງານສູງ ແລະອຸນຫະພູມສູງ—ເຮັດໃຫ້ເວເຟີ SiC ເປັນຊັ້ນຮອງທີ່ເລືອກສຳລັບສະຖານີຖານ 5G ລຸ້ນຕໍ່ໄປ ແລະລະບົບ radar. -

ວັດສະດຸ Optoelectronic ແລະ LED ຈາກ SiC Wafer

ໄຟ LED ສີຟ້າ ແລະ UV ທີ່ປູກຢູ່ເທິງຊັ້ນວາງແຜ່ນ SiC ໄດ້ຮັບຜົນປະໂຫຍດຈາກການຈັບຄູ່ແບບຕາຂ່າຍ ແລະ ການລະບາຍຄວາມຮ້ອນທີ່ດີເລີດ. ການໃຊ້ແຜ່ນ SiC ທີ່ມີໜ້າຮູບຕົວ C ຂັດເງົາຮັບປະກັນຊັ້ນ epitaxial ທີ່ສະໝໍ່າສະເໝີ, ໃນຂະນະທີ່ຄວາມແຂງຂອງແຜ່ນ SiC ຊ່ວຍໃຫ້ແຜ່ນບາງລົງ ແລະ ການຫຸ້ມຫໍ່ອຸປະກອນທີ່ໜ້າເຊື່ອຖືໄດ້. ສິ່ງນີ້ເຮັດໃຫ້ແຜ່ນ SiC ເປັນແພລດຟອມທີ່ນິຍົມໃຊ້ສຳລັບການນຳໃຊ້ LED ທີ່ມີພະລັງງານສູງ ແລະ ມີອາຍຸການໃຊ້ງານຍາວນານ.

ຄຳຖາມ ແລະ ຄຳຕອບກ່ຽວກັບແຜ່ນຊີຊີ

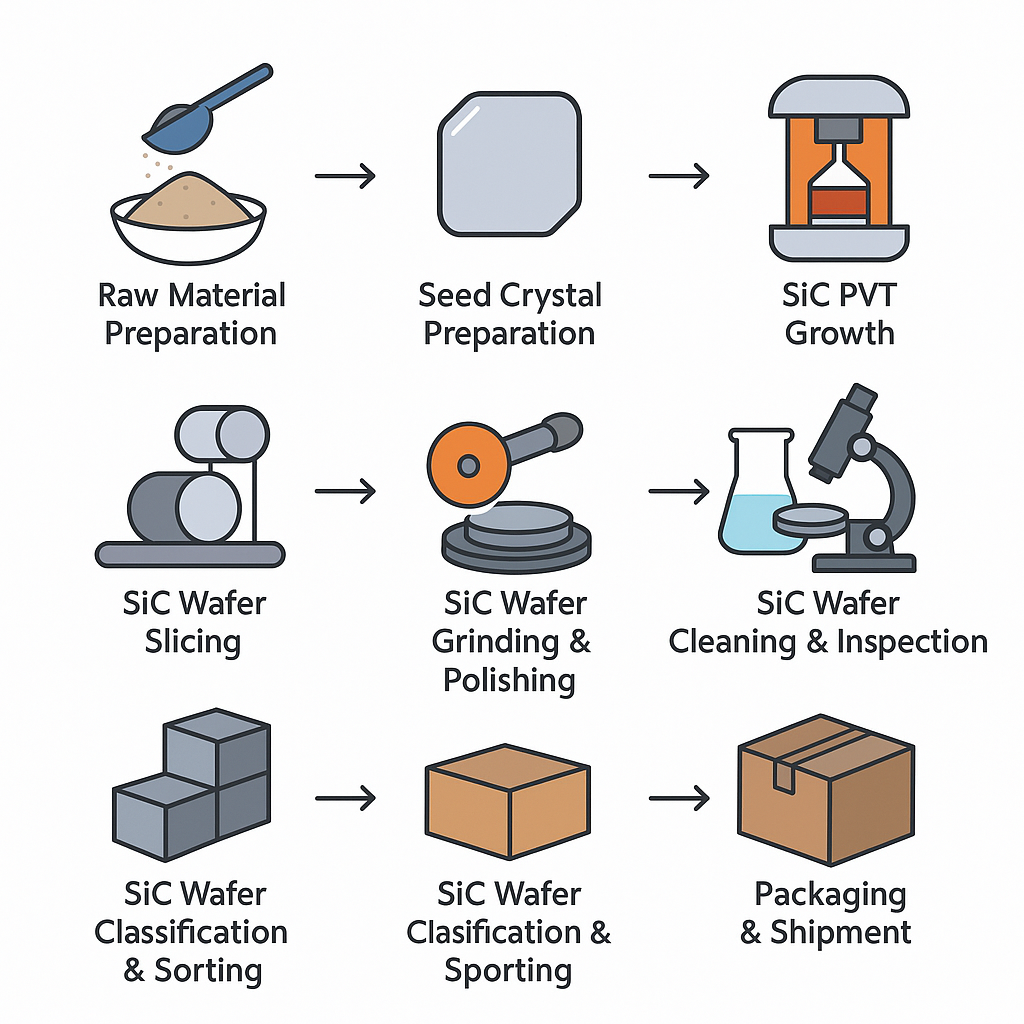

1. ຖາມ: ແຜ່ນຊິລິໂຄນຖືກຜະລິດແນວໃດ?

ກ:

ຜະລິດແຜ່ນຊີໄອຊີຂັ້ນຕອນລະອຽດ

-

ເວເຟີ SiCການກະກຽມວັດຖຸດິບ

- ໃຊ້ຜົງ SiC ເກຣດ ≥5N (ສິ່ງເຈືອປົນ ≤1 ppm).

- ຊອຍ ແລະ ອົບກ່ອນເພື່ອກຳຈັດສານປະກອບຄາບອນ ຫຼື ໄນໂຕຣເຈນທີ່ຍັງເຫຼືອ.

-

ຊີຊີການກະກຽມເມັດພັນໄປເຊຍກັນ

-

ເອົາຊິ້ນສ່ວນຂອງຜລຶກແກ້ວດ່ຽວ 4H-SiC, ຕັດຕາມທິດທາງ 〈0001〉 ເຖິງ ~10 × 10 ມມ².

-

ການຂັດເງົາຢ່າງແມ່ນຍໍາເຖິງ Ra ≤0.1 nm ແລະ ໝາຍທິດທາງຂອງຜລຶກ.

-

-

ຊີຊີການເຕີບໂຕຂອງ PVT (ການຂົນສົ່ງໄອທາງກາຍະພາບ)

-

ໃສ່ຖ້ວຍແກ້ວແກຣໄຟ: ຢູ່ດ້ານລຸ່ມດ້ວຍຜົງ SiC, ຢູ່ດ້ານເທິງດ້ວຍເມັດແກ້ວ.

-

ລະບາຍຄວາມຮ້ອນໄປສູ່ອຸນຫະພູມ 10⁻³–10⁻⁵ ຫຼື ຕື່ມດ້ວຍຮີລຽມທີ່ມີຄວາມບໍລິສຸດສູງທີ່ 1 atm.

-

ອຸນຫະພູມເຂດແຫຼ່ງຄວາມຮ້ອນໃຫ້ຢູ່ທີ່ 2100–2300 ℃, ຮັກສາເຂດເມັດພັນໃຫ້ເຢັນລົງ 100–150 ℃.

-

ຄວບຄຸມອັດຕາການເຕີບໂຕທີ່ 1–5 ມມ/ຊົ່ວໂມງ ເພື່ອດຸ່ນດ່ຽງຄຸນນະພາບ ແລະ ປະລິມານການຜະລິດ.

-

-

ຊີຊີການອົບໂລຫະ

-

ອົບກ້ອນ SiC ທີ່ເຕີບໃຫຍ່ແລ້ວໃຫ້ຮ້ອນທີ່ 1600–1800 ℃ ເປັນເວລາ 4–8 ຊົ່ວໂມງ.

-

ຈຸດປະສົງ: ບັນເທົາຄວາມກົດດັນທາງຄວາມຮ້ອນ ແລະ ຫຼຸດຜ່ອນຄວາມໜາແໜ້ນຂອງການເຄື່ອນທີ່.

-

-

ຊີຊີຊອຍແຜ່ນເວເຟີ

-

ໃຊ້ເລື່ອຍລວດເພັດເພື່ອຊອຍແທ່ງໂລຫະໃຫ້ເປັນແຜ່ນບາງໆໜາ 0.5–1 ມມ.

-

ຫຼຸດຜ່ອນການສັ່ນສະເທືອນ ແລະ ແຮງຂ້າງຄຽງເພື່ອຫຼີກລ່ຽງຮອຍແຕກຂະໜາດນ້ອຍ.

-

-

ຊີຊີເວເຟີການຂັດ ແລະ ການຂັດເງົາ

-

ການບົດຫຍາບເພື່ອກຳຈັດຄວາມເສຍຫາຍຈາກການເລື່ອຍ (ຄວາມຫຍາບ ~10–30 µm).

-

ການບົດລະອຽດເພື່ອໃຫ້ບັນລຸຄວາມຮາບພຽງ ≤5 µm.

-

ການຂັດເງົາທາງເຄມີ-ກົນຈັກ (CMP)ເພື່ອໃຫ້ໄດ້ຜິວໜ້າທີ່ຄ້າຍຄືກະຈົກ (Ra ≤0.2 nm).

-

-

ຊີຊີເວເຟີການເຮັດຄວາມສະອາດ ແລະ ການກວດກາ

-

ການເຮັດຄວາມສະອາດດ້ວຍຄື້ນສຽງໃນການແກ້ໄຂ Piranha (H₂SO₄:H₂O₂), ນ້ຳ DI, ຈາກນັ້ນ IPA.

-

ການສະແກນສະເປກໂຕຣສະໂຄປີ XRD/ຣາມັນເພື່ອຢືນຢັນ polytype (4H, 6H, 3C).

-

ການໂຕ້ຕອບເພື່ອວັດແທກຄວາມຮາບພຽງ (<5 µm) ແລະ ຄວາມໂຄ້ງງໍ (<20 µm).

-

ໂພຣບສີ່ຈຸດເພື່ອທົດສອບຄວາມຕ້ານທານ (ຕົວຢ່າງ HPSI ≥10⁹ Ω·cm).

-

ການກວດສອບຂໍ້ບົກພ່ອງກ້ອງຈຸລະທັດພາຍໃຕ້ແສງຂົ້ວ ແລະ ເຄື່ອງທົດສອບຮອຍຂີດຂ່ວນ.

-

-

ຊີຊີເວເຟີການຈັດປະເພດ ແລະ ການຈັດຮຽງ

-

ຈັດຮຽງແຜ່ນເວເຟີຕາມປະເພດໂພລີໄທບ ແລະ ປະເພດໄຟຟ້າ:

-

ປະເພດ 4H-SiC N (4H-N): ຄວາມເຂັ້ມຂຸ້ນຂອງຕົວນຳ 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC ຄວາມບໍລິສຸດສູງເຄິ່ງສນວນ (4H-HPSI): ຄວາມຕ້ານທານ ≥10⁹ Ω·cm

-

ປະເພດ 6H-SiC N (6H-N)

-

ອື່ນໆ: 3C-SiC, P-type, ແລະອື່ນໆ.

-

-

-

ຊີຊີເວເຟີການຫຸ້ມຫໍ່ ແລະ ການຂົນສົ່ງ

2. ຖາມ: ຂໍ້ໄດ້ປຽບຫຼັກຂອງແຜ່ນ SiC ທຽບກັບແຜ່ນຊິລິໂຄນແມ່ນຫຍັງ?

ກ: ເມື່ອປຽບທຽບກັບແຜ່ນຊິລິໂຄນ, ແຜ່ນ SiC ຊ່ວຍໃຫ້:

-

ການເຮັດວຽກແຮງດັນໄຟຟ້າທີ່ສູງຂຶ້ນ(>1,200 V) ດ້ວຍຄວາມຕ້ານທານຕໍ່ອິນເຕີເນັດຕ່ຳ.

-

ສະຖຽນລະພາບອຸນຫະພູມສູງຂຶ້ນ(>300 °C) ແລະ ປັບປຸງການຄຸ້ມຄອງຄວາມຮ້ອນ.

-

ຄວາມໄວໃນການປ່ຽນໄວຂຶ້ນດ້ວຍການສູນເສຍການສະຫຼັບຕ່ຳກວ່າ, ຫຼຸດຜ່ອນຄວາມເຢັນໃນລະດັບລະບົບ ແລະ ຂະໜາດໃນຕົວແປງພະລັງງານ.

4. ຖາມ: ຂໍ້ບົກຜ່ອງທົ່ວໄປອັນໃດທີ່ສົ່ງຜົນກະທົບຕໍ່ຜົນຜະລິດ ແລະ ປະສິດທິພາບຂອງແຜ່ນຊີດີເວເຟີ SiC?

ກ: ຂໍ້ບົກຜ່ອງຫຼັກໃນແຜ່ນ SiC ປະກອບມີທໍ່ຂະໜາດນ້ອຍ, ການເຄື່ອນທີ່ຂອງແຜ່ນພື້ນຖານ (BPDs), ແລະ ຮອຍຂີດຂ່ວນເທິງໜ້າດິນ. ທໍ່ຂະໜາດນ້ອຍສາມາດເຮັດໃຫ້ເກີດຄວາມລົ້ມເຫຼວຂອງອຸປະກອນທີ່ຮ້າຍແຮງ; BPDs ເພີ່ມຄວາມຕ້ານທານຕໍ່ເນື່ອງໄປຕາມການເວລາ; ແລະ ຮອຍຂີດຂ່ວນເທິງໜ້າດິນນຳໄປສູ່ການແຕກຫັກຂອງແຜ່ນ wafer ຫຼື ການເຕີບໂຕຂອງ epitaxial ທີ່ບໍ່ດີ. ດັ່ງນັ້ນ, ການກວດກາຢ່າງເຂັ້ມງວດ ແລະ ການຫຼຸດຜ່ອນຂໍ້ບົກຜ່ອງຈຶ່ງມີຄວາມຈຳເປັນເພື່ອເພີ່ມຜົນຜະລິດແຜ່ນ SiC ໃຫ້ສູງສຸດ.

ເວລາໂພສ: 30 ມິຖຸນາ 2025