ຖາມ: ເຕັກໂນໂລຊີຫຼັກທີ່ໃຊ້ໃນການຊອຍ ແລະ ປຸງແຕ່ງແຜ່ນຊິລິໂຄນແມ່ນຫຍັງ?

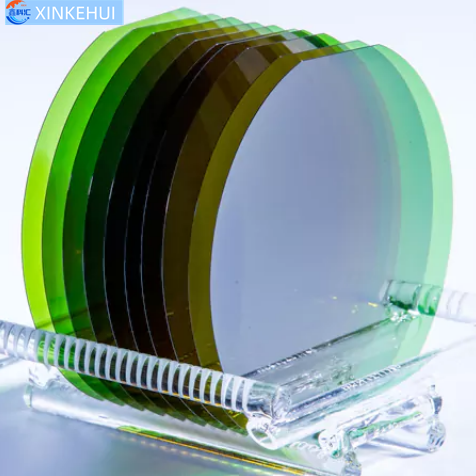

A:ຊິລິກອນຄາໄບ (SiC) ມີຄວາມແຂງເປັນອັນດັບສອງຮອງຈາກເພັດ ແລະ ຖືກຖືວ່າເປັນວັດສະດຸທີ່ແຂງ ແລະ ແຕກງ່າຍຫຼາຍ. ຂະບວນການຊອຍ, ເຊິ່ງກ່ຽວຂ້ອງກັບການຕັດຜລຶກທີ່ເຕີບໃຫຍ່ແລ້ວໃຫ້ເປັນແຜ່ນບາງໆ, ແມ່ນໃຊ້ເວລາຫຼາຍ ແລະ ມີແນວໂນ້ມທີ່ຈະແຕກ. ໃນຖານະເປັນຂັ້ນຕອນທຳອິດໃນຊີຊີການປຸງແຕ່ງຜລຶກດຽວ, ຄຸນນະພາບຂອງການຊອຍມີອິດທິພົນຢ່າງຫຼວງຫຼາຍຕໍ່ການບົດ, ການຂັດ, ແລະ ການເຮັດໃຫ້ບາງລົງໃນພາຍຫຼັງ. ການຊອຍມັກຈະເຮັດໃຫ້ເກີດຮອຍແຕກເທິງໜ້າດິນ ແລະ ໃຕ້ໜ້າດິນ, ເຊິ່ງເຮັດໃຫ້ອັດຕາການແຕກຂອງແຜ່ນເວເຟີ ແລະ ຕົ້ນທຶນການຜະລິດເພີ່ມຂຶ້ນ. ດັ່ງນັ້ນ, ການຄວບຄຸມຄວາມເສຍຫາຍຂອງຮອຍແຕກເທິງໜ້າດິນໃນລະຫວ່າງການຊອຍແມ່ນມີຄວາມສຳຄັນຫຼາຍຕໍ່ການພັດທະນາການຜະລິດອຸປະກອນ SiC.

ວິທີການຕັດ SiC ທີ່ລາຍງານໃນປະຈຸບັນປະກອບມີການຂັດແບບຄົງທີ່, ການຕັດແບບເສລີ, ການຕັດດ້ວຍເລເຊີ, ການໂອນຊັ້ນ (ການແຍກເຢັນ), ແລະ ການຕັດແບບປ່ອຍໄຟຟ້າ. ໃນບັນດາສິ່ງເຫຼົ່ານີ້, ການຕັດຫຼາຍສາຍແບບກັບກັນດ້ວຍສານຂັດເພັດຄົງທີ່ແມ່ນວິທີການທີ່ນິຍົມໃຊ້ຫຼາຍທີ່ສຸດສຳລັບການປຸງແຕ່ງຜລຶກ SiC ດ່ຽວ. ຢ່າງໃດກໍຕາມ, ຍ້ອນວ່າຂະໜາດຂອງແທ່ງໂລຫະມີຂະໜາດເຖິງ 8 ນິ້ວຂຶ້ນໄປ, ການເລື່ອຍສາຍແບບດັ້ງເດີມຈຶ່ງໃຊ້ບໍ່ໄດ້ຜົນເນື່ອງຈາກຄວາມຕ້ອງການອຸປະກອນສູງ, ຄ່າໃຊ້ຈ່າຍ, ແລະ ປະສິດທິພາບຕ່ຳ. ມີຄວາມຕ້ອງການອັນຮີບດ່ວນສຳລັບເຕັກໂນໂລຊີການຕັດທີ່ມີລາຄາຖືກ, ການສູນເສຍຕ່ຳ, ແລະ ປະສິດທິພາບສູງ.

ຄຳຖາມ: ຂໍ້ດີຂອງການຊອຍດ້ວຍເລເຊີທຽບກັບການຕັດຫຼາຍສາຍແບບດັ້ງເດີມແມ່ນຫຍັງ?

ກ: ການເລື່ອຍລວດແບບດັ້ງເດີມຈະຕັດແທ່ງ SiCຕາມທິດທາງສະເພາະໃດໜຶ່ງໃຫ້ເປັນຕ່ອນໜາຫຼາຍຮ້ອຍໄມຄຣອນ. ຫຼັງຈາກນັ້ນ, ຕ່ອນເຫຼົ່ານັ້ນຈະຖືກບົດໂດຍໃຊ້ນ້ຳຢາສະກັດເພັດເພື່ອກຳຈັດຮອຍເລື່ອຍ ແລະ ຄວາມເສຍຫາຍໃຕ້ພື້ນຜິວ, ຕາມດ້ວຍການຂັດດ້ວຍເຄມີກົນຈັກ (CMP) ເພື່ອໃຫ້ໄດ້ແຜ່ນລຽບ, ແລະ ສຸດທ້າຍເຮັດຄວາມສະອາດເພື່ອໃຫ້ໄດ້ແຜ່ນ SiC.

ເຖິງຢ່າງໃດກໍ່ຕາມ, ເນື່ອງຈາກຄວາມແຂງ ແລະ ຄວາມແຕກງ່າຍຂອງ SiC, ຂັ້ນຕອນເຫຼົ່ານີ້ສາມາດເຮັດໃຫ້ເກີດການບິດເບືອນ, ການແຕກ, ອັດຕາການແຕກຫັກເພີ່ມຂຶ້ນ, ຕົ້ນທຶນການຜະລິດທີ່ສູງຂຶ້ນ, ແລະ ເຮັດໃຫ້ເກີດຄວາມຫຍາບ ແລະ ການປົນເປື້ອນຂອງພື້ນຜິວສູງ (ຂີ້ຝຸ່ນ, ນ້ຳເສຍ, ແລະອື່ນໆ). ນອກຈາກນັ້ນ, ການເລື່ອຍລວດຍັງຊ້າ ແລະ ມີຜົນຜະລິດຕໍ່າ. ການຄາດຄະເນສະແດງໃຫ້ເຫັນວ່າການຕັດລວດຫຼາຍເສັ້ນແບບດັ້ງເດີມບັນລຸການນໍາໃຊ້ວັດສະດຸພຽງແຕ່ປະມານ 50%, ແລະ ວັດສະດຸສູງເຖິງ 75% ຈະສູນເສຍໄປຫຼັງຈາກການຂັດ ແລະ ບົດ. ຂໍ້ມູນການຜະລິດຕ່າງປະເທດໃນຕອນຕົ້ນຊີ້ໃຫ້ເຫັນວ່າມັນອາດຈະໃຊ້ເວລາປະມານ 273 ມື້ຂອງການຜະລິດ 24 ຊົ່ວໂມງຢ່າງຕໍ່ເນື່ອງເພື່ອຜະລິດເວເຟີ 10,000 ແຜ່ນ - ໃຊ້ເວລາຫຼາຍ.

ຢູ່ພາຍໃນປະເທດ, ບໍລິສັດຜະລິດຜລຶກ SiC ຫຼາຍແຫ່ງແມ່ນສຸມໃສ່ການເພີ່ມກຳລັງການຜະລິດຂອງເຕົາອົບ. ຢ່າງໃດກໍຕາມ, ແທນທີ່ຈະພຽງແຕ່ຂະຫຍາຍຜົນຜະລິດ, ມັນມີຄວາມສຳຄັນຫຼາຍກວ່າທີ່ຈະພິຈາລະນາວິທີການຫຼຸດຜ່ອນການສູນເສຍ - ໂດຍສະເພາະເມື່ອຜົນຜະລິດຂອງຜລຶກຍັງບໍ່ທັນດີທີ່ສຸດ.

ອຸປະກອນຕັດດ້ວຍເລເຊີສາມາດຫຼຸດຜ່ອນການສູນເສຍວັດສະດຸ ແລະ ປັບປຸງຜົນຜະລິດໄດ້ຢ່າງຫຼວງຫຼາຍ. ຕົວຢ່າງ, ການໃຊ້ທໍ່ຕັດຂະໜາດ 20 ມມ ອັນດຽວແທ່ງ SiCການເລື່ອຍລວດສາມາດໃຫ້ຜົນຜະລິດໄດ້ປະມານ 30 ແຜ່ນທີ່ມີຄວາມໜາ 350 μm. ການຊອຍດ້ວຍເລເຊີສາມາດໃຫ້ຜົນຜະລິດໄດ້ຫຼາຍກວ່າ 50 ແຜ່ນ. ຖ້າຄວາມໜາຂອງແຜ່ນຖືກຫຼຸດລົງເຫຼືອ 200 μm, ສາມາດຜະລິດແຜ່ນໄດ້ຫຼາຍກວ່າ 80 ແຜ່ນຈາກແທ່ງດຽວກັນ. ໃນຂະນະທີ່ການເລື່ອຍລວດຖືກນຳໃຊ້ຢ່າງກວ້າງຂວາງສຳລັບແຜ່ນຂະໜາດ 6 ນິ້ວ ແລະ ນ້ອຍກວ່າ, ການຊອຍແທ່ງ SiC ຂະໜາດ 8 ນິ້ວອາດໃຊ້ເວລາ 10-15 ມື້ດ້ວຍວິທີການແບບດັ້ງເດີມ, ຕ້ອງການອຸປະກອນລະດັບສູງ ແລະ ມີຄ່າໃຊ້ຈ່າຍສູງແຕ່ມີປະສິດທິພາບຕ່ຳ. ພາຍໃຕ້ເງື່ອນໄຂເຫຼົ່ານີ້, ຂໍ້ໄດ້ປຽບຂອງການຊອຍດ້ວຍເລເຊີຈະກາຍເປັນທີ່ຊັດເຈນ, ເຮັດໃຫ້ມັນກາຍເປັນເທັກໂນໂລຢີອະນາຄົດຫຼັກສຳລັບແຜ່ນຂະໜາດ 8 ນິ້ວ.

ດ້ວຍການຕັດດ້ວຍເລເຊີ, ເວລາໃນການຊອຍຕໍ່ເວເຟີຂະໜາດ 8 ນິ້ວສາມາດຕໍ່າກວ່າ 20 ນາທີ, ໂດຍມີການສູນເສຍວັດສະດຸຕໍ່ເວເຟີຕໍ່າກວ່າ 60 μm.

ສະຫຼຸບແລ້ວ, ເມື່ອປຽບທຽບກັບການຕັດຫຼາຍສາຍ, ການຕັດດ້ວຍເລເຊີໃຫ້ຄວາມໄວສູງກວ່າ, ຜົນຜະລິດດີກວ່າ, ການສູນເສຍວັດສະດຸຕ່ຳກວ່າ, ແລະ ການປະມວນຜົນທີ່ສະອາດກວ່າ.

ຖາມ: ສິ່ງທ້າທາຍທາງດ້ານເຕັກນິກຫຼັກໃນການຕັດເລເຊີ SiC ແມ່ນຫຍັງ?

ກ: ຂະບວນການຕັດເລເຊີກ່ຽວຂ້ອງກັບສອງຂັ້ນຕອນຫຼັກຄື: ການດັດແປງເລເຊີ ແລະ ການແຍກແຜ່ນເວເຟີ.

ຫຼັກຂອງການດັດແປງເລເຊີແມ່ນການສ້າງຮູບຮ່າງຂອງລຳແສງ ແລະ ການເພີ່ມປະສິດທິພາບຂອງພາລາມິເຕີ. ພາລາມິເຕີຕ່າງໆເຊັ່ນ: ພະລັງງານເລເຊີ, ເສັ້ນຜ່າສູນກາງຂອງຈຸດ, ແລະ ຄວາມໄວໃນການສະແກນລ້ວນແຕ່ມີຜົນກະທົບຕໍ່ຄຸນນະພາບຂອງການກຳຈັດວັດສະດຸ ແລະ ຄວາມສຳເລັດຂອງການແຍກແຜ່ນເວເຟີຕໍ່ມາ. ຮູບຮ່າງຂອງເຂດທີ່ຖືກດັດແປງກຳນົດຄວາມຫຍາບຂອງພື້ນຜິວ ແລະ ຄວາມຫຍຸ້ງຍາກໃນການແຍກ. ຄວາມຫຍາບຂອງພື້ນຜິວສູງເຮັດໃຫ້ການບົດໃນພາຍຫຼັງສັບສົນ ແລະ ເພີ່ມການສູນເສຍວັດສະດຸ.

ຫຼັງຈາກການດັດແປງ, ການແຍກແຜ່ນເວເຟີໂດຍທົ່ວໄປແມ່ນບັນລຸໄດ້ໂດຍຜ່ານແຮງຕັດ, ເຊັ່ນ: ການແຕກຫັກດ້ວຍຄວາມເຢັນ ຫຼື ຄວາມກົດດັນທາງກົນຈັກ. ລະບົບພາຍໃນປະເທດບາງລະບົບໃຊ້ຕົວປ່ຽນຄວາມຖີ່ສູງເພື່ອກະຕຸ້ນການສັ່ນສະເທືອນສຳລັບການແຍກ, ແຕ່ສິ່ງນີ້ສາມາດເຮັດໃຫ້ເກີດການບิ่น ແລະ ຂໍ້ບົກຜ່ອງຂອງຂອບ, ເຊິ່ງເຮັດໃຫ້ຜົນຜະລິດສຸດທ້າຍຫຼຸດລົງ.

ໃນຂະນະທີ່ສອງຂັ້ນຕອນເຫຼົ່ານີ້ບໍ່ມີຄວາມຫຍຸ້ງຍາກໂດຍທຳມະຊາດ, ຄວາມບໍ່ສອດຄ່ອງກັນໃນຄຸນນະພາບຂອງຜລຶກ - ເນື່ອງຈາກຂະບວນການເຕີບໃຫຍ່, ລະດັບການເສີມ, ແລະການແຈກຢາຍຄວາມກົດດັນພາຍໃນທີ່ແຕກຕ່າງກັນ - ສົ່ງຜົນກະທົບຢ່າງຫຼວງຫຼາຍຕໍ່ຄວາມຫຍຸ້ງຍາກໃນການຊອຍ, ຜົນຜະລິດ, ແລະການສູນເສຍວັດສະດຸ. ພຽງແຕ່ການລະບຸພື້ນທີ່ທີ່ມີບັນຫາ ແລະ ການປັບເຂດການສະແກນເລເຊີອາດຈະບໍ່ປັບປຸງຜົນໄດ້ຮັບຢ່າງຫຼວງຫຼາຍ.

ກຸນແຈສຳຄັນໃນການຮັບຮອງເອົາຢ່າງກວ້າງຂວາງແມ່ນການພັດທະນາວິທີການ ແລະ ອຸປະກອນທີ່ມີນະວັດຕະກໍາທີ່ສາມາດປັບຕົວເຂົ້າກັບຄຸນນະພາບຂອງຜລຶກທີ່ຫຼາກຫຼາຍຈາກຜູ້ຜະລິດຕ່າງໆ, ການເພີ່ມປະສິດທິພາບຂອງຕົວກໍານົດການຂະບວນການ, ແລະ ການສ້າງລະບົບການຕັດເລເຊີທີ່ສາມາດນໍາໃຊ້ໄດ້ທົ່ວໄປ.

ຖາມ: ເຕັກໂນໂລຊີການຕັດເລເຊີສາມາດນຳໃຊ້ກັບວັດສະດຸເຄິ່ງຕົວນຳອື່ນໆນອກຈາກ SiC ໄດ້ບໍ?

ກ: ເທັກໂນໂລຢີການຕັດດ້ວຍເລເຊີໄດ້ຖືກນຳໃຊ້ກັບວັດສະດຸຫຼາກຫຼາຍຊະນິດໃນອະດີດ. ໃນເຄິ່ງຕົວນຳ, ໃນເບື້ອງຕົ້ນມັນຖືກໃຊ້ສຳລັບການຫັ່ນແຜ່ນເວເຟີ ແລະ ນັບຕັ້ງແຕ່ນັ້ນມາໄດ້ຂະຫຍາຍໄປສູ່ການຫັ່ນຜລຶກກ້ອນໃຫຍ່.

ນອກເໜືອໄປຈາກ SiC, ການຊອຍດ້ວຍເລເຊີຍັງສາມາດໃຊ້ສຳລັບວັດສະດຸແຂງ ຫຼື ແຕກຫັກງ່າຍອື່ນໆເຊັ່ນ: ເພັດ, ແກລຽມໄນໄຕຣດ (GaN), ແລະ ແກລຽມອົກໄຊດ໌ (Ga₂O₃). ການສຶກສາເບື້ອງຕົ້ນກ່ຽວກັບວັດສະດຸເຫຼົ່ານີ້ໄດ້ສະແດງໃຫ້ເຫັນເຖິງຄວາມເປັນໄປໄດ້ ແລະ ຂໍ້ດີຂອງການຊອຍດ້ວຍເລເຊີສຳລັບການນຳໃຊ້ເຄິ່ງຕົວນຳ.

ຖ: ປະຈຸບັນມີຜະລິດຕະພັນອຸປະກອນຕັດເລເຊີພາຍໃນປະເທດທີ່ພັດທະນາແລ້ວບໍ? ການຄົ້ນຄວ້າຂອງທ່ານຢູ່ໃນຂັ້ນຕອນໃດ?

ກ: ອຸປະກອນຕັດເລເຊີ SiC ເສັ້ນຜ່າສູນກາງຂະໜາດໃຫຍ່ຖືກພິຈາລະນາຢ່າງກວ້າງຂວາງວ່າເປັນອຸປະກອນຫຼັກສຳລັບອະນາຄົດຂອງການຜະລິດແຜ່ນ SiC ຂະໜາດ 8 ນິ້ວ. ປະຈຸບັນ, ມີພຽງແຕ່ປະເທດຍີ່ປຸ່ນເທົ່ານັ້ນທີ່ສາມາດສະໜອງລະບົບດັ່ງກ່າວໄດ້, ແລະພວກມັນມີລາຄາແພງ ແລະ ມີຂໍ້ຈຳກັດດ້ານການສົ່ງອອກ.

ຄວາມຕ້ອງການພາຍໃນປະເທດສຳລັບລະບົບການຕັດ/ການເຮັດໃຫ້ບາງລົງດ້ວຍເລເຊີຄາດວ່າຈະຢູ່ທີ່ປະມານ 1,000 ໜ່ວຍ, ໂດຍອີງໃສ່ແຜນການຜະລິດ SiC ແລະ ກຳລັງການຜະລິດຂອງເລື່ອຍສາຍທີ່ມີຢູ່ແລ້ວ. ບໍລິສັດພາຍໃນປະເທດທີ່ສຳຄັນໄດ້ລົງທຶນຢ່າງຫຼວງຫຼາຍໃນການພັດທະນາ, ແຕ່ຍັງບໍ່ມີອຸປະກອນພາຍໃນປະເທດທີ່ເຕີບໃຫຍ່ເຕັມທີ່ ແລະ ມີໃຫ້ບໍລິການທາງການຄ້າທີ່ບັນລຸການນຳໃຊ້ໃນອຸດສາຫະກຳເທື່ອ.

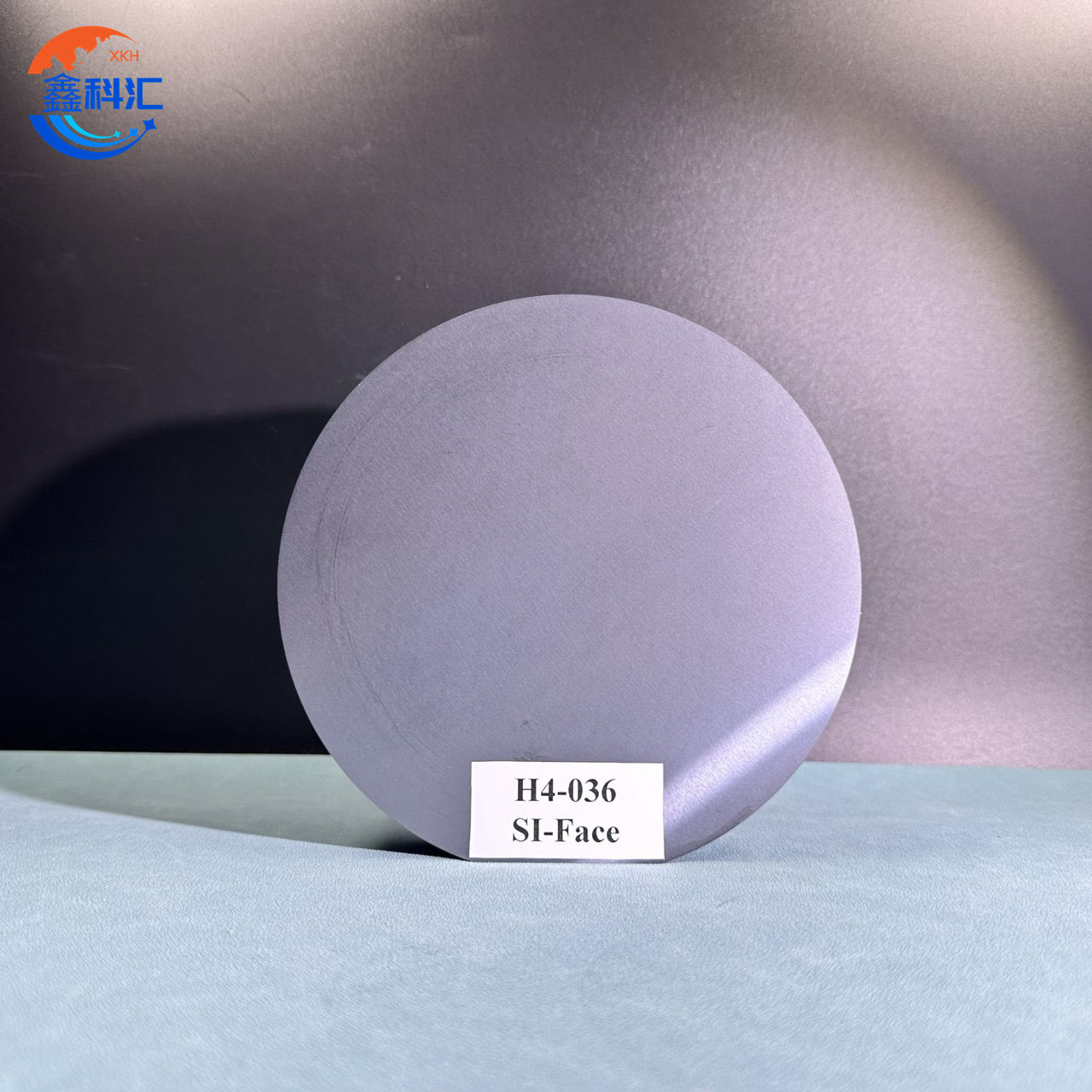

ກຸ່ມຄົ້ນຄວ້າໄດ້ພັດທະນາເທັກໂນໂລຢີການຍົກດ້ວຍເລເຊີທີ່ເປັນເຈົ້າຂອງຕັ້ງແຕ່ປີ 2001 ແລະປະຈຸບັນໄດ້ຂະຫຍາຍສິ່ງນີ້ໄປສູ່ການຊອຍ ແລະ ການບາງລົງດ້ວຍເລເຊີ SiC ທີ່ມີເສັ້ນຜ່າສູນກາງຂະໜາດໃຫຍ່. ພວກເຂົາໄດ້ພັດທະນາລະບົບຕົ້ນແບບ ແລະ ຂະບວນການຊອຍທີ່ມີຄວາມສາມາດໃນການ: ການຕັດ ແລະ ການບາງລົງດ້ວຍເວເຟີ SiC ເຄິ່ງສນວນ ຂະໜາດ 4–6 ນິ້ວ ການຊອຍແທ່ງ SiC ທີ່ນຳໄຟຟ້າ ຂະໜາດ 6–8 ນິ້ວ ມາດຕະຖານການປະຕິບັດ: SiC ເຄິ່ງສນວນ ຂະໜາດ 6–8 ນິ້ວ: ເວລາຊອຍ 10–15 ນາທີ/ເວເຟີ; ການສູນເສຍວັດສະດຸ <30 μm SiC ທີ່ນຳໄຟຟ້າ 6–8 ນິ້ວ: ເວລາຊອຍ 14–20 ນາທີ/ເວເຟີ; ການສູນເສຍວັດສະດຸ <60 μm

ຜົນຜະລິດຂອງແຜ່ນເວເຟີທີ່ຄາດຄະເນໄວ້ເພີ່ມຂຶ້ນຫຼາຍກວ່າ 50%

ຫຼັງຈາກຕັດແລ້ວ, ເວເຟີຕອບສະໜອງມາດຕະຖານແຫ່ງຊາດສຳລັບຮູບຮ່າງເລຂາຄະນິດຫຼັງຈາກການບົດ ແລະ ຂັດ. ການສຶກສາຍັງສະແດງໃຫ້ເຫັນວ່າຜົນກະທົບທາງຄວາມຮ້ອນທີ່ເກີດຈາກເລເຊີບໍ່ໄດ້ສົ່ງຜົນກະທົບຕໍ່ຄວາມຕຶງຄຽດ ຫຼື ຮູບຮ່າງເລຂາຄະນິດໃນເວເຟີຢ່າງຫຼວງຫຼາຍ.

ອຸປະກອນດຽວກັນນີ້ຍັງຖືກນໍາໃຊ້ເພື່ອກວດສອບຄວາມເປັນໄປໄດ້ສໍາລັບການຕັດເພັດ, GaN, ແລະຜລຶກແກ້ວດ່ຽວ Ga₂O₃.

ເວລາໂພສ: ພຶດສະພາ-23-2025